IBM DeveloperWorks AIX Virtual User Group February 18<sup>th</sup>, 2016 webinar

# The IBM Power8 Processor Core Microarchitecture

(a white paper summary with thoughts and considerations)

Prepared and Edited by Earl Jew (not an author of the whitepaper) <u>earlj@us.ibm.com</u>; (310) 251-2907; Los Angeles, California, USA Senior IT Consultant for IBM Power Systems and System Storage IBM STG Lab Services Power Systems Delivery Practice

## ABSTRACT

The POWER8 processor is the latest RISC (Reduced Instruction Set Computer) microprocessor from IBM. It is fabricated using the company's 22-nm Silicon on Insulator (SOI) technology with 15 layers of metal, and it has been designed to significantly improve both single-thread performance and single-core throughput over its predecessor, the POWER7 processor.

The rate of increase in processor frequency enabled by new silicon technology advancements has decreased dramatically in recent generations, as compared to the historic trend. This has caused many processor designs in the industry to show very little improvement in either single-thread or single-core performance, and, instead, larger numbers of cores are primarily pursued in each generation.

Going against this industry trend, the POWER8 processor relies on a much improved core and nest microarchitecture to achieve approximately one-and-a-half times the single-thread performance and twice the single-core throughput of the POWER7 processor in several commercial applications. Combined with a 50% increase in the number of cores (from 8 in the POWER7 processor to 12 in the POWER8 processor), the result is a processor that leads the industry in performance for enterprise workloads.

This paper describes the core microarchitecture innovations made in the POWER8 processor that resulted in these significant performance benefits.

Based on the article by the same title in

IBM JOURNAL OF RESEARCH & DEVELOPMENT VOL. 59 NO. 1 PAPER 2 JANUARY/FEBRUARY 2015

Written by B. Sinharoy, J. A. Van Norstrand, R. J. Eickemeyer, H. Q. Le, J. Leenstra, D. Q. Nguyen, B. Konigsburg, K. Ward, M. D. Brown, J. E. Moreira, D. Levitan, S. Tung, D. Hrusecky, J. W. Bishop, M. Gschwind, M. Boersma, M. Kroener, M. Kaltenbach, T. Karkhanis, K. M. Fernsler

## Presenter Commentary Caveat

- This presentation is an intermix of excerpts/figures from the original whitepaper and presenter commentary.

- The blue borders designate Presenter Commentary (like this slide).

- The presenter's comments are based solely on the words of the whitepaper, and do not offer any insider's insight beyond the content of this whitepaper.

- Please judge the presenter's thoughts and considerations accordingly.

- That is, I don't know anything more than what we all can read together here.

This paper describes the core microarchitecture innovations made in the POWER8 processor that resulted in these significant performance benefits.

Based on principles adopted in the POWER7 multi-core processor, the POWER8 processor continues to emphasize **a balanced multi-core design**, with <u>significant improvements in both single-thread and core performance</u> and modest increases in the core count per chip.

This contrasts with other multi-core processor designs in the industry today, for which an increase in the core count is primarily pursued with little improvement in single-thread or core performance.

In this eighth-generation POWER processor, IBM continues to innovate its RISC (Reduced Instruction Set Computer) product line by introducing a twelve-core multi-chip design, with large on-chip eDRAM (embedded Dynamic Random Access Memory) caches, and high-performance eight-way multi-threaded cores, implementing the Power ISA (Instruction Set Architecture) version 2.07. Our goal for the POWER8 processor was to significantly improve the socketlevel, core-level and thread-level performance in each of the multiple simultaneous multithreading (SMT) modes relative to the POWER7 processor.

This was achieved by keeping the area and power requirement of each POWER8 processor core (POWER8 core) sufficiently low to allow twelve such cores on the processor chip while maintaining its power at the same level as that of the POWER7 processor chip.

- Regarding "to significantly improve the socket-level, core-level and thread-level performance in each of the multiple simultaneous multithreading (SMT) modes", because there are as many as 12 CPUcores per socket (which is a tremendous amount of processing capacity), configuring an LPAR to reside on only one socket that accesses only local DIMMs should be a pervasive POWER8 imperative given its ideal performance advantages.

- **Tight&Fat:** Configure fewer vCPUs, grant 0.7-0.9 eCPU per vCPU, and drive the core-level harder with SMT-2/4/8 thread-level workloads on POWER8.

- View/confirm any configuration with **AIX:lssrad** -av output.

- Study&practice using the Dynamic Platform Optimizer (DPO) utility.

An at-a-glance comparison between the POWER7 and the POWER8 processors can be seen in Table 1.

**Table 1**Summary of characteristics of the POWER7and POWER8 processors.

|                                   | POWER7 | POWER8 |

|-----------------------------------|--------|--------|

| Cores/chip                        | 8      | 12     |

| Maximum threads/core              | 4      | 8      |

| L1 instruction cache/core         | 32 KB  | 32 KB  |

| L1 data cache/core                | 32 KB  | 64 KB  |

| L2 cache/core                     | 256 KB | 512 KB |

| L3 cache/core                     | 4 MB   | 8 MB   |

| Instruction issue/cycle/core      | 8      | 10     |

| Instruction completion/cycle/core | 6      | 8      |

Because of the slowdown in frequency increases from silicon technology, thread and core performance were improved through micro-architectural enhancements such as an:

- advanced branch prediction mechanism

- extensive out-of-order execution

- dual pipelines for instruction decode, dispatch, issue, and execution

- advanced eight-way simultaneous multi-threading

- advanced prefetching with more precise application software control over the prefetching mechanism

- doubled bandwidth throughout the cache and memory hierarchy

- a significant reduction in memory latency relative to the POWER7 processor design

Many business analytics applications run in **thread-rich configurations**, to exploit the inherent parallelism in these computations. To accommodate them, **the POWER8 core doubled the hardware thread parallelism to 8-way multithreading (referred to as SMT8)**.

Because of the doubling in size of the L1 data cache and L2 and L3 caches, each thread in a POWER8 core can have as much resident memory footprint as a thread in a POWER7 core.

In fact, it was a **design requirement** that at each common multithreading level -- ST (single-thread), SMT2 (two-way multithreading), and SMT4 (fourway multithreading) -- **the individual thread performance on a POWER8 core should be better than on a POWER7 core.**

## In single-thread mode, practically all of the core resources can be used by the single thread.

At the same time, these core resources can efficiently support eight threads per core. The core can dynamically change mode among ST, SMT2, SMT4, and SMT8, depending on the number of active threads. Cloud instances often do not have enough simultaneously active application threads to utilize all eight hardware threads on the POWER8 core.

To instead exploit the parallelism across cloud instances, the POWER8 core can be put in a "split-core mode", so that four partitions can run on one core at the same time, with up to two hardware threads per partition.

- This knocked my socks off!! This means a vCPU in SMT-2 mode from four different LPARs can run <u>concurrently</u> on a given POWER8 core.

- In other words, four LPARs can have a vCPU in SMT-2 mode running on the same POWER8 core at the same time.

- For tuning, it means <u>vCPU time-slice fragmentation</u> (the 4<sup>th</sup> Dimension of Affinity) could eventually be partially mitigated by use of split-core mode.

- This POWER8 capability is also called "micro-threading".

- I believe this is only offered with PowerKVM, i.e. redbook:<u>IBM PowerKVM</u> <u>Configuration and Use</u> (sg248231.pdf Oct 2014)

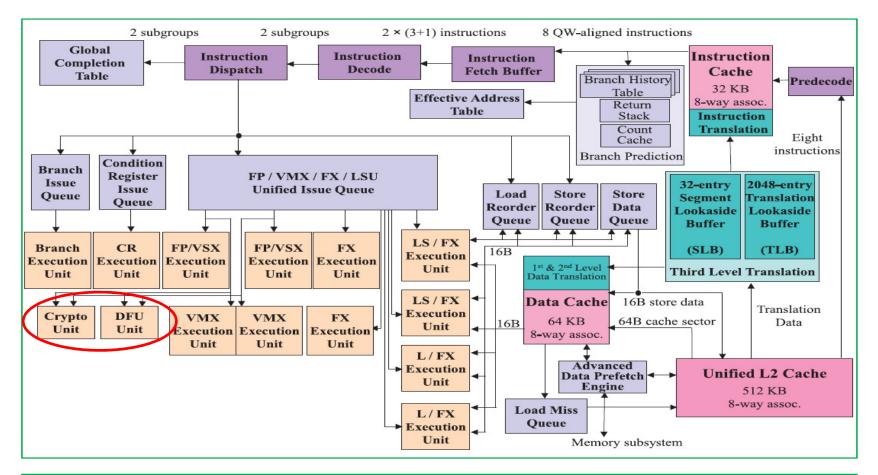

Modern computing environments, and **cloud systems in particular, require extra layers of security and protection** in order to deliver a safe and usable solution to the end user.

For that reason, the POWER8 processor includes several features that accelerate cryptographic codes.

In particular, the POWER8 core includes a cryptographic unit supporting new Power ISA instructions for the computation of AES (Advanced Encryption Standard), SHA (Secure Hash Algorithm), and CRC (Cyclic Redundancy Check) codes.

The IBM 4764 PCI-X Cryptographic Coprocessor was withdrawn in 2011. **Overview**

The IBM PCI-X Cryptographic Coprocessor provides a highsecurity, high-throughput cryptographic subsystem. The tamperresponding hardware is validated at the highest level under the stringent FIPS PUB (Federal Information Processing Standards Publication) 140-2 standard. Specialized hardware performs AES, DES, TDES, RSA, and SHA-1 cryptographic processes, relieving the main processor from these tasks. The coprocessor design protects your cryptographic keys and sensitive custom

applications. The software running in the coprocessor can be customized to meet special requirements.

Big data applications typically have a larger memory footprint and working set than traditional commercial applications. Correspondingly, compared to the POWER7 core, the POWER8 core has an <u>L1 data cache</u> that is twice as large, has twice as many ports from that data cache for higher read/write throughput, and has four times as many entries in its TLB (Translation Lookaside Buffer).

In addition, POWER8 technology expands the addressing range of memory accesses using fusion to allow applications to access large data sets more quickly. As mentioned, **the L2 and L3 caches in the POWER8 processor are also twice the size** of the corresponding POWER7 processor caches, on a per core basis.

- The trend of POWER engineering is clearly about keeping more data closer with 2 times larger L1 data cache and 2 times larger L2 and L3 caches.

- Having twice as many ports from that data cache for higher read/write throughput means moving more data faster to the 16 execution pipelines.

- Having four times as many entries in its TLB (Translation Lookaside Buffer) means cache-speed address translations. The TLB is a cache of address translations. Any TLB miss means searching the hardware page table (HPT; residing on slower main memory) for the missed address translation.

- Keeping Tight&Fat on one socket substantially improves all of the above.

## Optimally exploiting the POWER8 core microarchitecture

- The best way to exploit POWER8/AIX is to first understand your workload with meaningful POWER/AIX tactical monitoring, i.e. "knowing it by the numbers".

- Open invitation: Write to me for my script and I promise to assist in this regard.

- Optimal exploitation doesn't always mean the fastest performance/throughput

- It may mean the most productivity-per-CPUcore or productivity-per-license

- It may mean the quickest responsiveness at the expense of wasted CPUcycles

- Sometimes you just care to understand what your workload is doing better

- Sometimes you want to learn what else can be done to improve a situation

- Other times there is a crisis and you urgently need another willing set-of-eyes

- Try me: Call or write and I will do what I can to help. Really truly, I'm real.

- I work for IBM Lab Services and Training; we're a different delivery practice

## IBM Systems Lab Services, U.S. Power AIX & LoP Offerings

Stephen Brandenburg – sbranden@us.ibm.com -OR- Linda Hoben – hoben@us.ibm.com -OR- Michael Gordon – mgordo@us.ibm.com

#### **Power Workshops**

- Power8 Transition Workshop

- NEW! Power8 Provisioning Assurance

- Power/AIX Monitoring and Tuning (not using NMON)

- IBM Power & Storage Planning for Disaster Recovery Workshop

- Data Center Availability Assessment

#### Power (VM) Virtual Management

- PowerVM HealthCheck / Best Practices Review

- PowerVM Customized Training (NPIV, LPM, AMS/AME, etc.)

- PowerVM Provisioning Toolkit (with NEW! "Capture" capability)

- IBM Proactive Monitoring for AIX & VIOS ("ProMon")

- NEW! PowerVM LPM Automation Tool (from China Labs team)

- Power Enterprise Pools Enablement

- WPAR (Workload Partition) Implementation and/or Migration

#### Power (HA) High Availability

- PowerHA Customized Training

- PowerHA SE Implementation / HealthCheck

- PowerHA & Storage Implementation for Disaster Recovery

- PowerHA EE Implementation for DR (incl. Toolkit "Capture")

#### **Power Performance**

- Power Virtualization Performance (PowerVP)

- Performance Optimization Assessment (POA)

- Oracle on AIX Performance Assessment Services

- Capacity Planning Tool (CPT) installation & configuration

- DB2 on AIX Application Performance Assessment (DB2 BLU)

- IBM Tivoli Monitoring (ITM) support for clients with AIX EE

#### **Big Data Enablement**

- IBM Power Analytics Infrastructure Enablement (DNS, DHCP, email, virus scanning, file sharing, etc.)

- BigData Assessment & Jumpstart Services

- Linux on Power BigData InfoSphere BigInsights

- Linux on Power BigData InfoSphere InfoStreams

- Linux on Power BigData Executive Infrastructure Review

#### Linux

- Power IFL Implementation

- Linux on Power (LoP) Customized Training

- IBM PowerKVM

- Linux on PowerVM

- Linux on PowerVM Performance / HealthCheck

- Linux Workloads Assessment Workshop

- NEW! Linux on Power education offerings to expand customer training beyond the 1-day jump-starts from ATS

- Field Programmable Gate Array (FPGA) Development Platform RPQ

#### Cloud

- Cloud Design Workshop for custom cloud enablement

- PowerVC Implementation as a Pre-req to CMO

- Cloud Manager with OpenStack (CMO) Implementation

- Cloud IT Optimization Assessment

- Advanced Cloud on Power Services

- IBM Smart Analytics Optimizer Enablement

- SAP Landscape Virtualization Management Design & Planning Workshop

- SAP Landscape Virtualization Management Implementation

- Other "Open Stack" Consulting Services

#### **SAP HANA on Power**

- Installation and POC

- Health Check Assessment

#### Security

- IBM AIX Security Assessment

- LDAP Integration including Pass-through Authentication (PTA)

- IBM PowerSC<sup>™</sup> Security & Automated Compliance Workshop

- PowerSC Trusted Firewall Workshop (TWR)

- PowerSC Trusted Surveyor Workshop (TS)

- AIX Auditing Workshop

- AIX Hacking Prevention Workshop

- Encrypted File System (EFS) Workshop

- Role Based Access Control (RBAC) Workshop/Support Services

IBM Systems Lab Services & Training - Power Systems

Services for AIX, i5OS, and Linux on Power

http://www.ibm.com/systems/services/labservices/platforms/labservices power.html

### Power/AIX Performance and Tuning Workshop (4.0-days on-site)

#### **Overview:**

- This offering aims to grow and exercise the Power/AIX tactical skills of its attendees through lectures and lab sessions on their live-running AIX servers. The lectures describe the AIX Virtual Memory Manager, Power7 and Power8 Affinity, tactics for indicating performance issues, and remedial tactics to resolve these issues.

- Throughout each lecture, the workshop illustrates its topics and tactics on the attendee's live-running Power/AIX LPARs as lab session exercises. As such, an incidental list of directly-observed and empirically-justified remedial tactics can be accumulated by each attendee as a by-product of the workshop.

- The workshop is intended as a decidedly interactive venue. The attendee's questions are addressed immediately.

#### WHO benefits from this workshop and WHY ?

- Clients with Power6/7/8 servers with AIX 6.1-7.2 LPARs housing workloads.

- Clients who care to monitor their Power/AIX workloads by the numbers.

- Clients with workloads they suspect are not executing optimally but have been unable to determine what and why.

- Historically, Power/AIX system administrators, database administrators, application administrators, storage administrators, and IT architects have all learned more than they could imagine in a 4.0-day workshop.

#### Duration

- 28 to 32 hours (depending on the ability to absorb rigorous content)

- 6 to 8 hours per day (does not include an hour for lunch)

- Request a conference room with a PC projector

- Request an authorized staffer to "putty" into your Power/AIX LPARs

#### **Delivery Details:**

This is a customer onsite offering consisting of standup lectures and highly interactive lab sessions to your live-running LPARs. Presentation handouts are provided in PowerPoint format.

Lecture/Lab Session titles:

Part One: A Tactical Overview of Power/AIX Virtual Memory Manager mechanisms

Part Two: The Four Dimensions of Power7/Power8 Affinity

Part Three: How to use Power/AIX Historical/Cumulative Statistics to Indicate Performance Issues

Part Four: How to use Power/AXI Real-time Statistics to Indicate Performance Issues

Part Five: Remedial Tactics for Performance Tuning the Indicated Issues of Power/AIX Workloads

Part Six: IBM Power8 Processor Core Microarchitecture: Thoughts and Considerations

Terms and Conditions: Actual Tasks, Deliverables, Service Estimates, and travel requirements vary with each client's environment. When we have reached a final agreement on the scope of your initiative and our level of assistance, a formal document describing our proposed work effort, costs, etc, will be presented for your approval and signature.

Linda Hoben – *Opportunity Manager* hoben@us.ibm.com 1-720-395-0556 Stephen Brandenburg – *Opportunity Manager* sbranden@us.ibm.com 1-301-240-2182

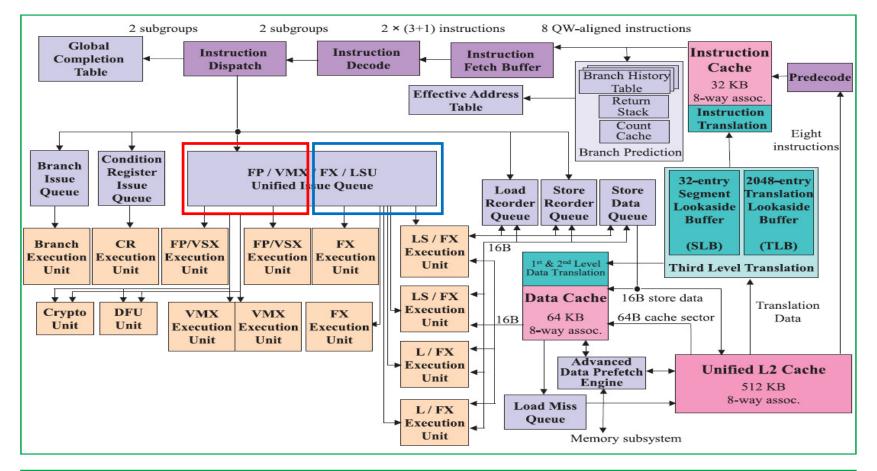

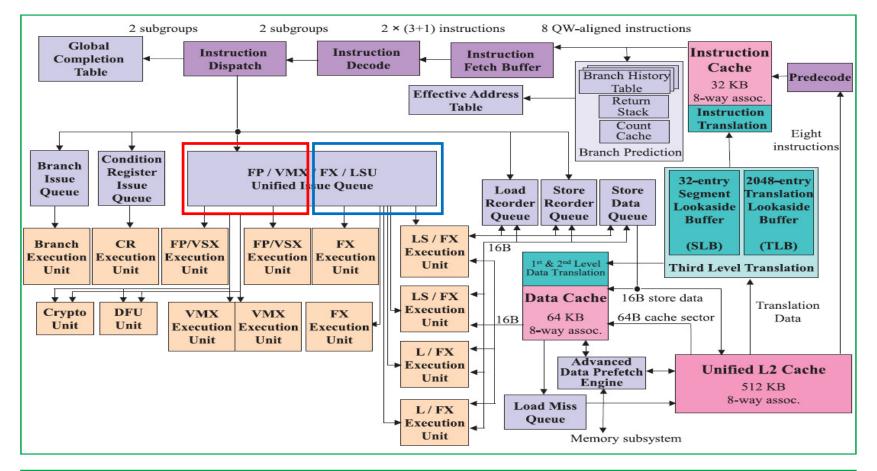

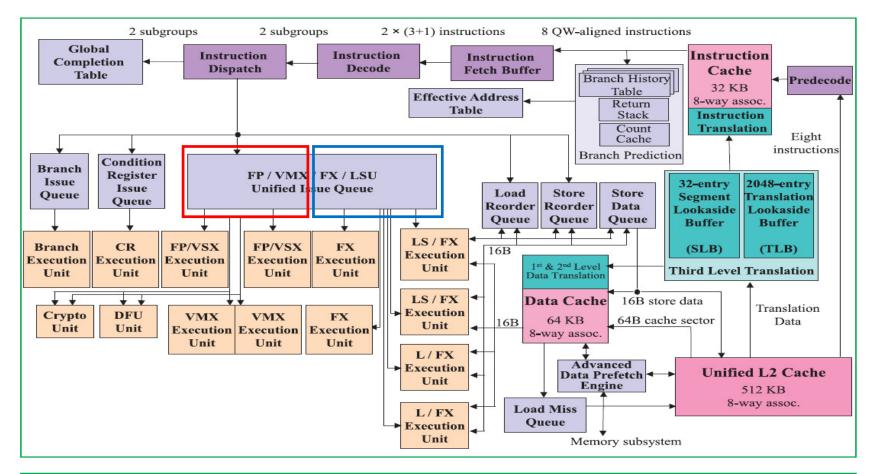

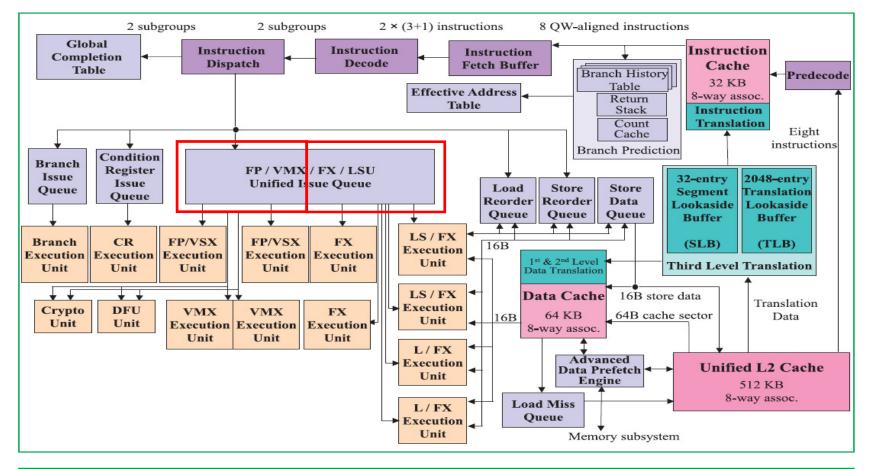

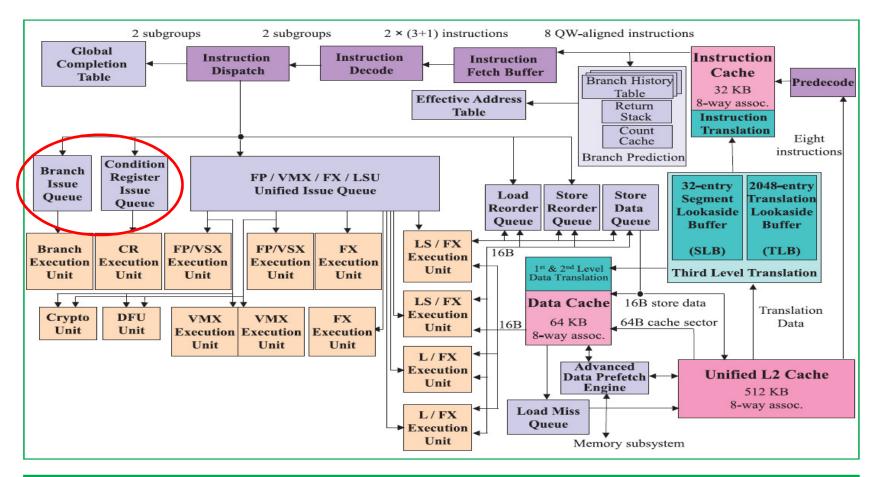

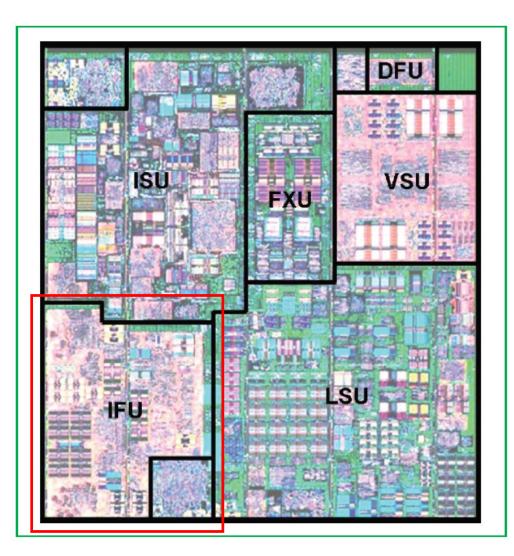

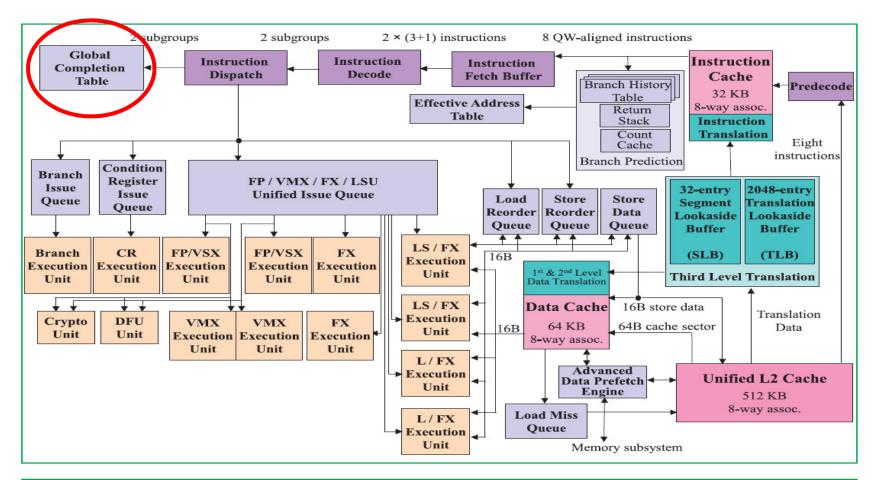

## **Organization of the POWER8 processor core**

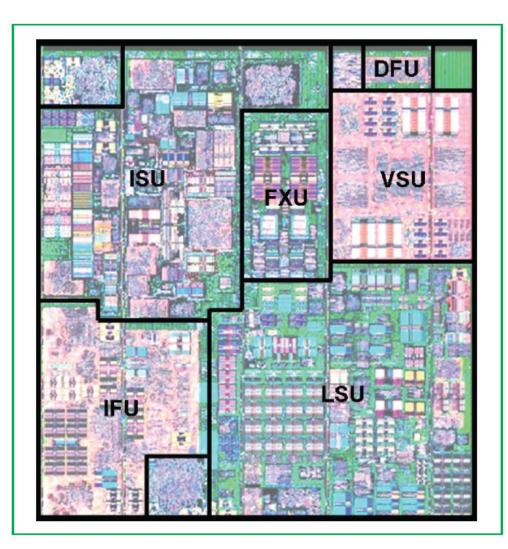

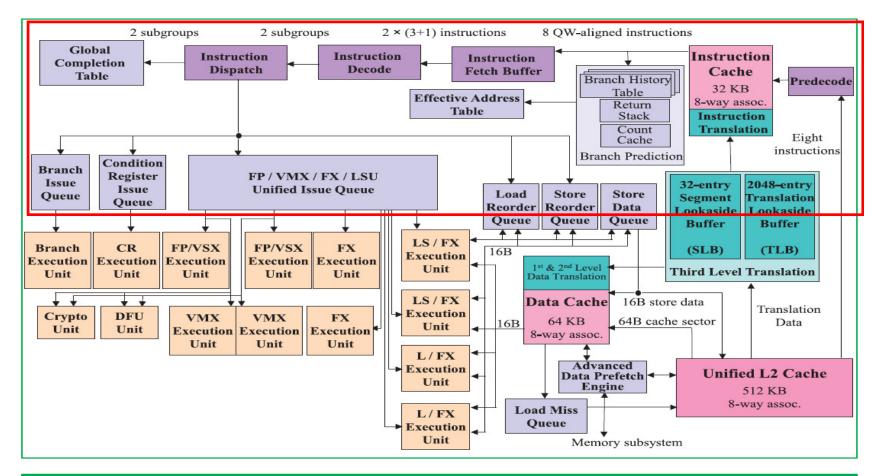

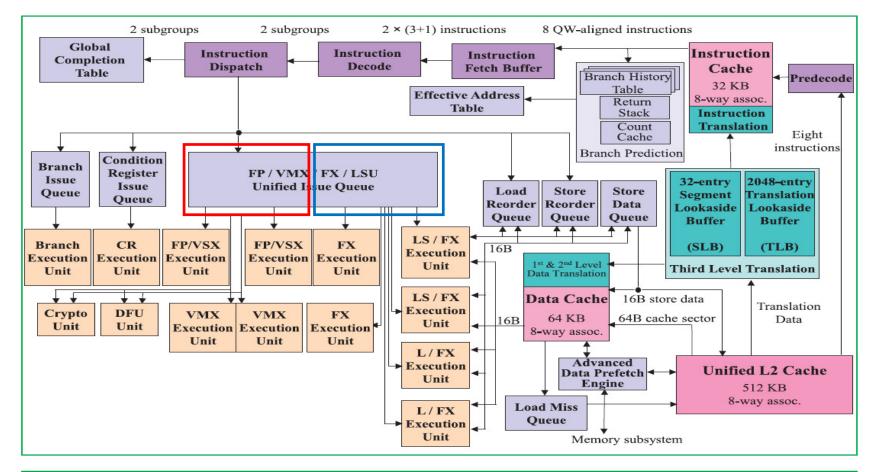

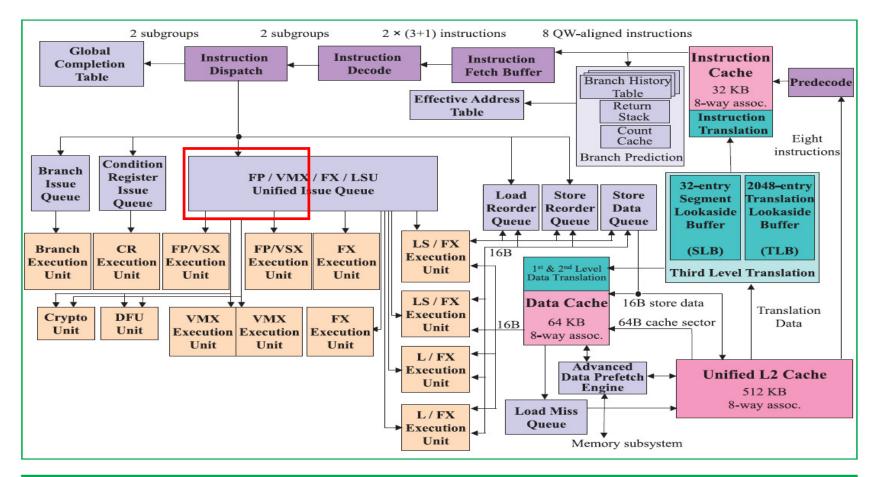

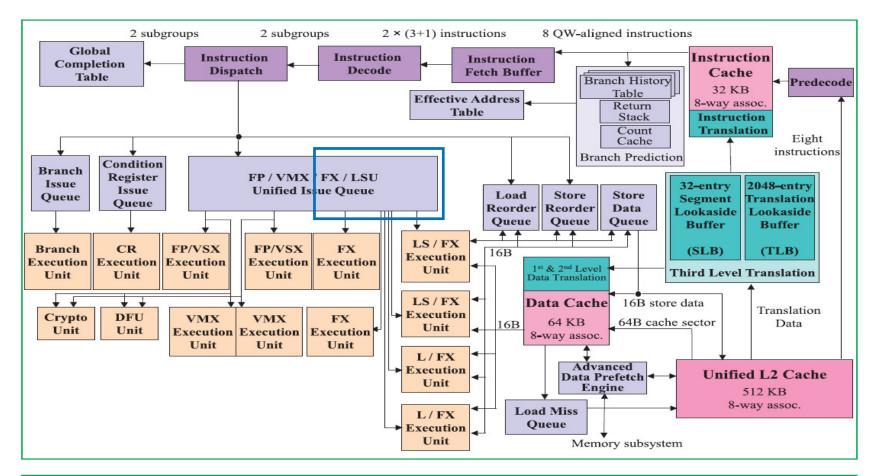

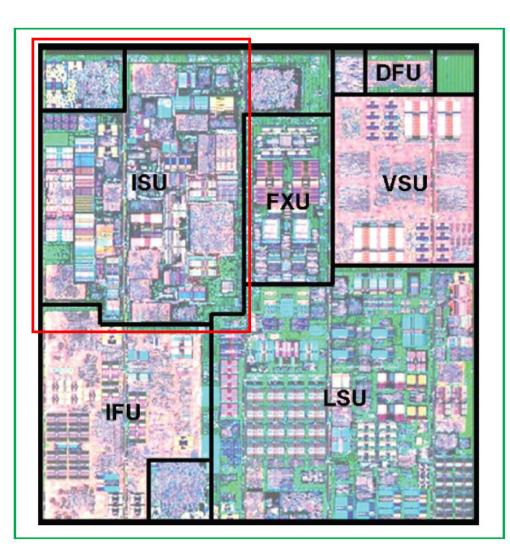

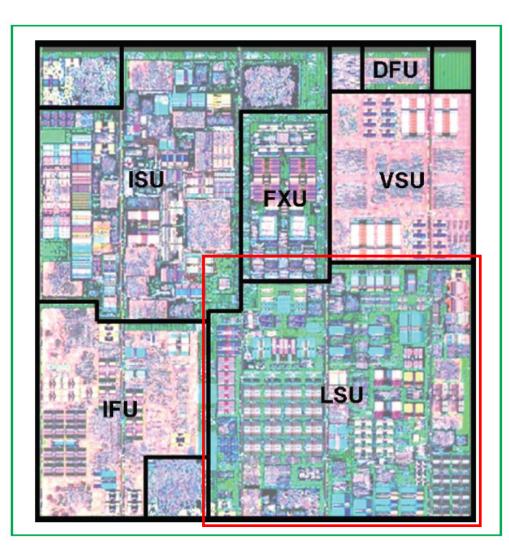

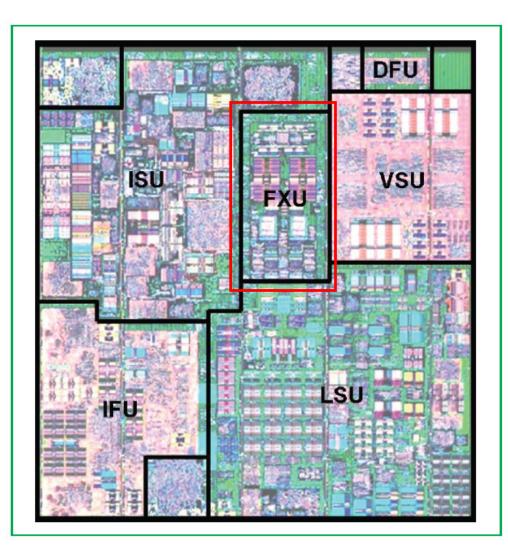

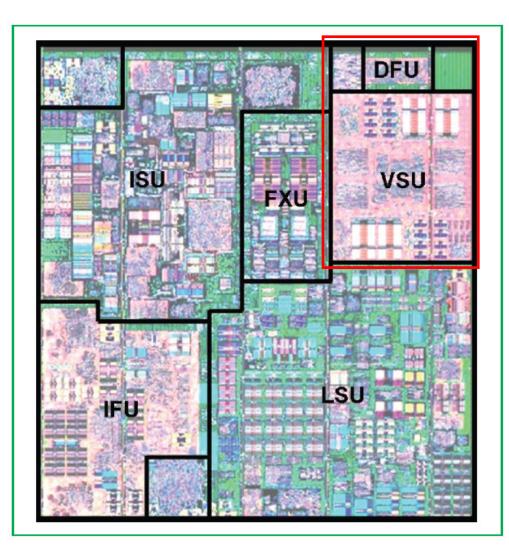

Figure 1 shows the POWER8 core floorplan.

The core consists primarily of the following six units: instruction fetch unit (IFU), instruction sequencing unit (ISU), load-store unit (LSU), fixed-point unit (FXU), vector and scalar unit (VSU) and decimal floating point unit (DFU).

The instruction fetch unit contains a 32 KB I-cache (instruction cache) and the load-store unit contains a 64 KB Dcache (data cache), which are both backed up by a tightly integrated 512 KB unified L2 cache.

### Figure 1

POWER8 processor core floorplan.

In a given cycle, the core can fetch up to eight instructions, decode and dispatch up to eight instructions, issue and execute up to ten instructions, and commit up to eight instructions.

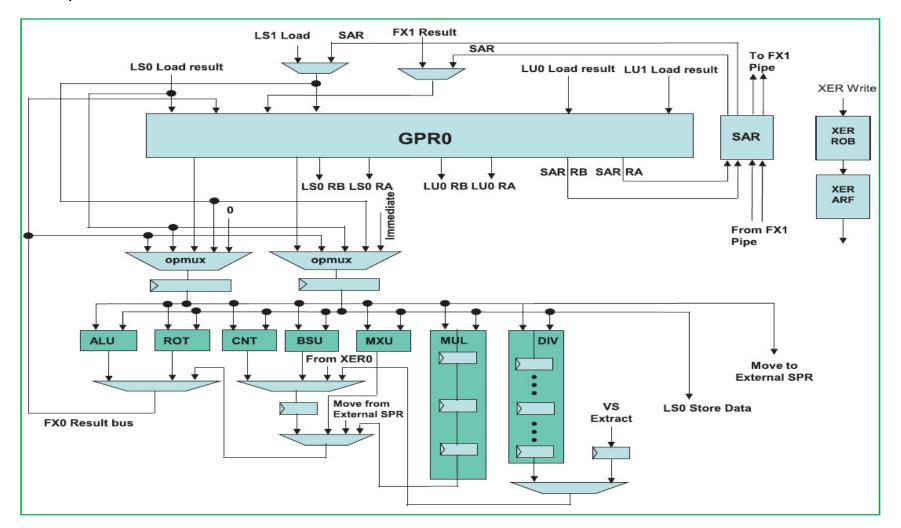

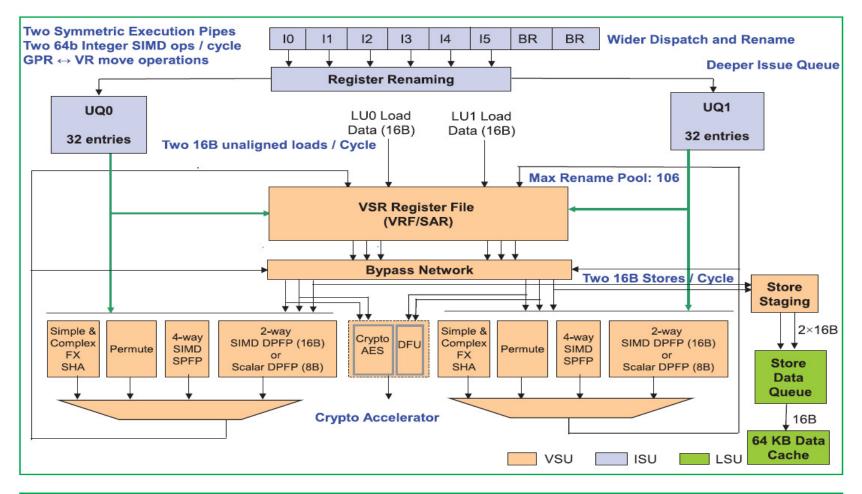

There are **sixteen execution pipelines** within the core:

- two fixed-point pipelines

- two load/store pipelines

- two load pipelines

- four double-precision floating-point pipelines (which can also act as eight single-precision floating-point pipelines)

- two fully symmetric vector pipelines that execute instructions from both the VMX (Vector eXtensions) and VSX (Vector-Scalar eXtensions) instruction categories in the Power ISA

- one cryptographic pipeline

- one branch execution pipeline

- one condition register logical pipeline

- one decimal floating-point pipeline

To satisfy the high bandwidth requirement of many commercial, big data, and HPC workloads, the POWER8 core has significantly higher load/store bandwidth capability compared to its predecessor.

While the POWER7 processor can perform two load/store operations in a given cycle, the POWER8 processor can perform two load operations in the load pipes, in addition to two load or store operations in the load/store pipes in a given cycle.

As was the case with the POWER7 processor, the large TLB of the POWER8 processor is not required to be invalidated on a partition swap. Instead, the **TLB entries can persist across partition swapping**, so that if a partition is swapped back again, some of its translation entries are likely to be found in the TLB.

Additionally, the POWER8 processor introduces a "partition prefetch" capability, which restores the cache state when a partition is swapped back into a processor core.

The POWER8 processor allows dynamic SMT mode switches among the various ST and SMT modes. The core supports the execution of up to eight hardware architected threads, named T0 through T7.

Unlike the POWER7 core, where the ST mode required the thread to run on the TO position, in the POWER8 core the single thread can run anywhere from TO to T7. As long as it is the only thread running, the core can execute in ST mode.

Similarly, as long as only two threads are running, the core can execute in SMT2 mode, and it does not matter which hardware thread positions those two threads are running.

This makes the SMT mode switch in the POWER8 core significantly easier and does not require software to invoke an expensive thread move operation to put the thread(s) in the right position to switch into the desired SMT mode.

In addition, the performance difference of running one single thread on the core when the core is in ST mode versus in any of the SMT modes is significantly lower in the POWER8 processor than in the POWER7 processor.

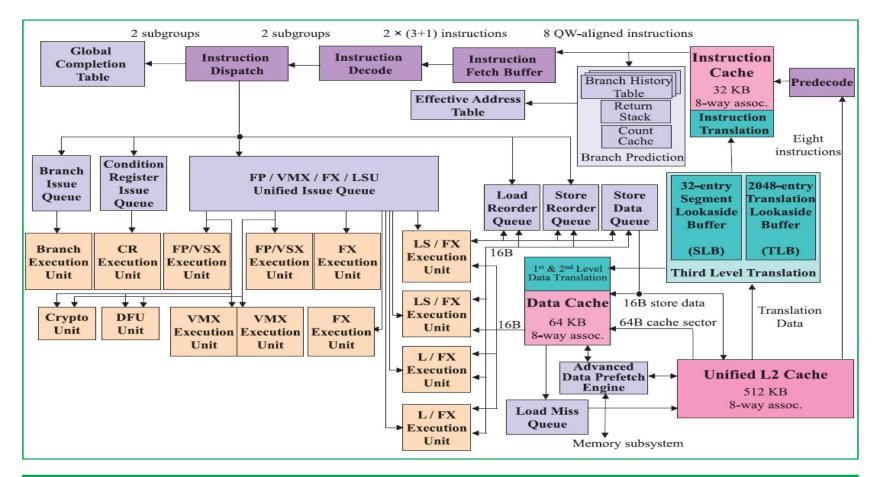

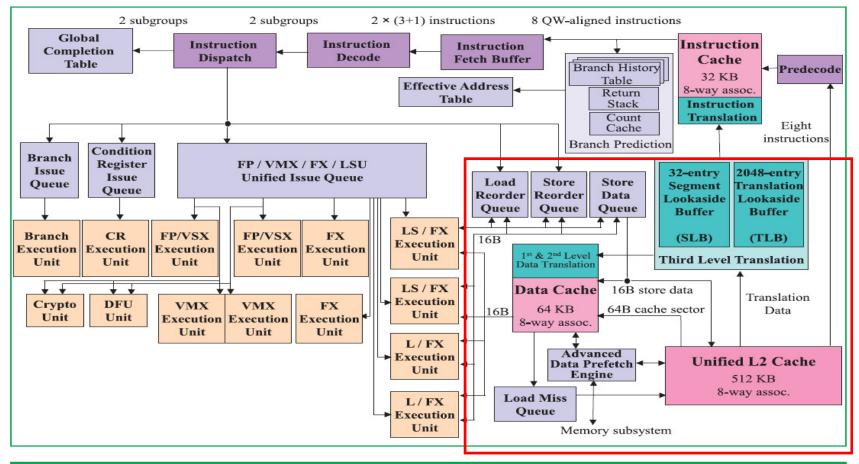

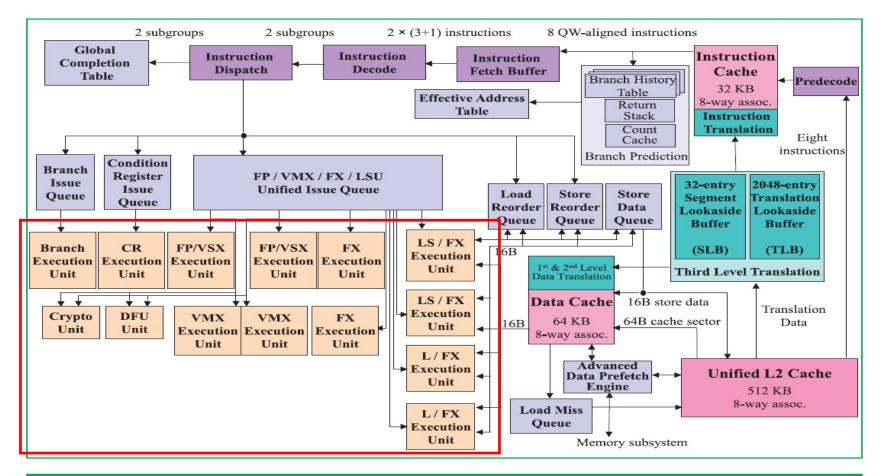

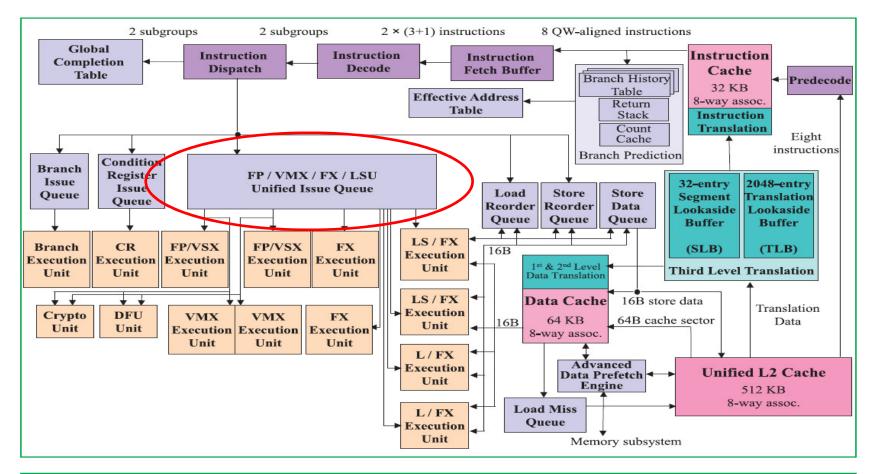

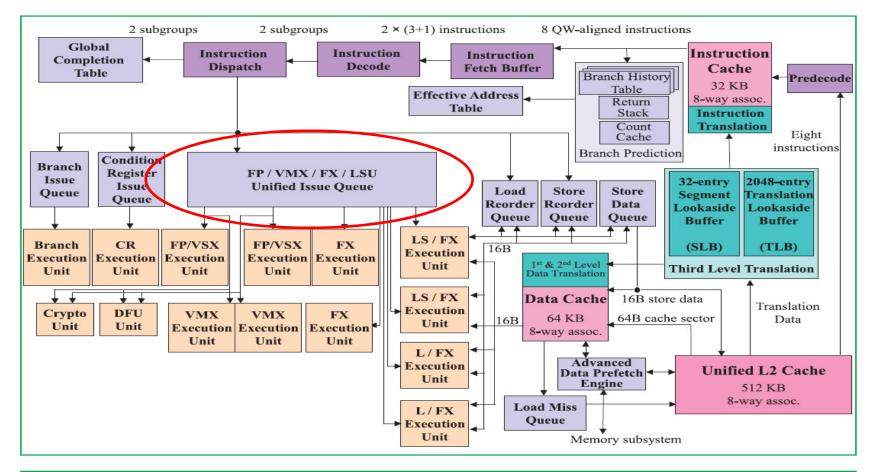

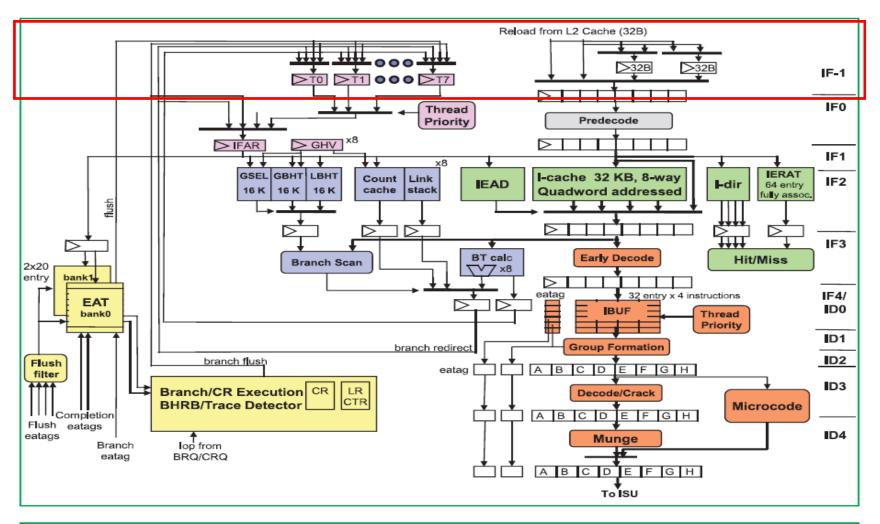

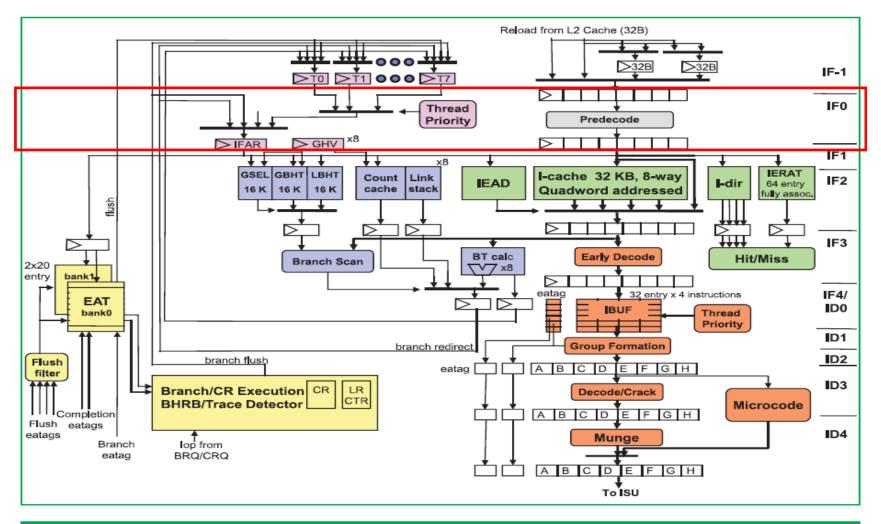

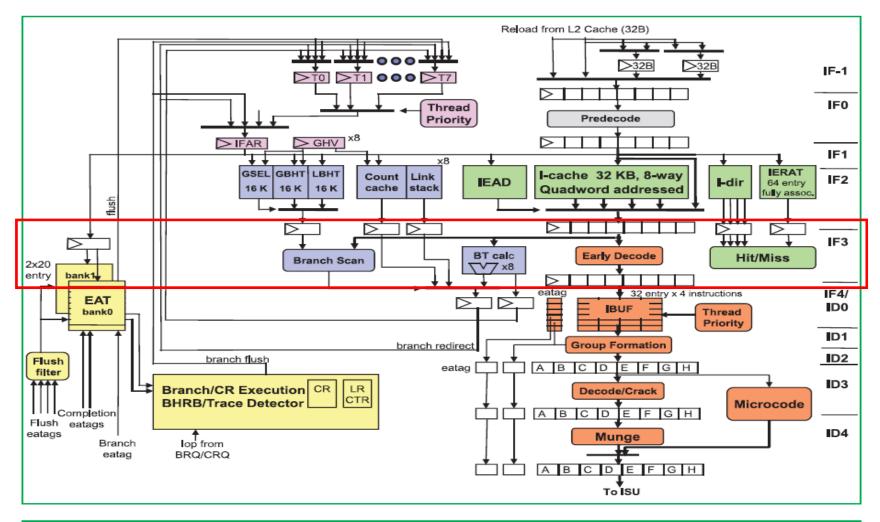

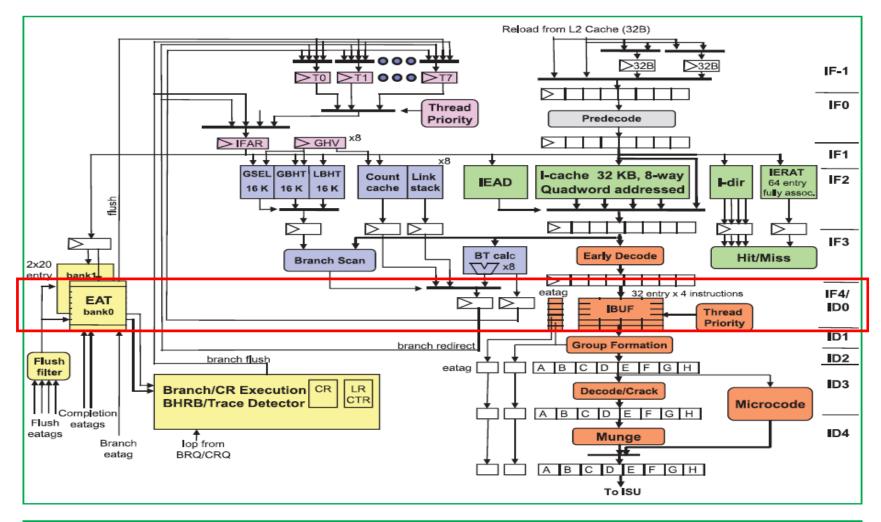

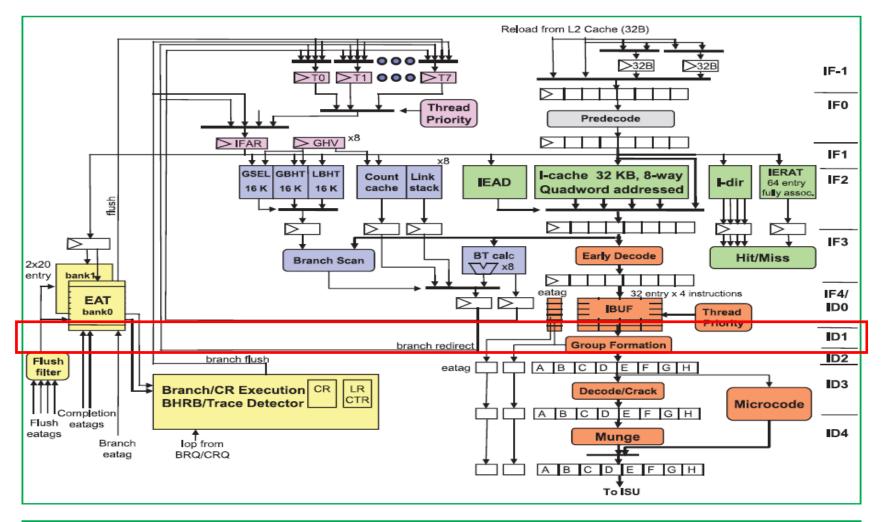

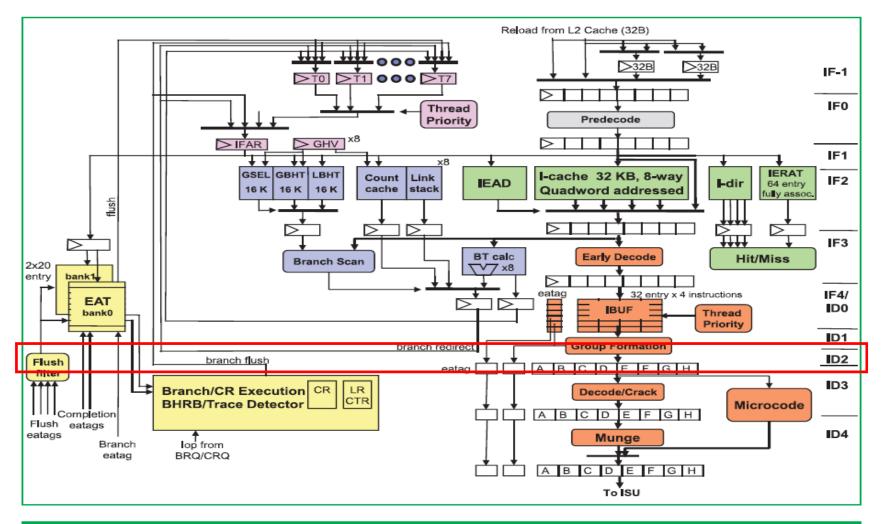

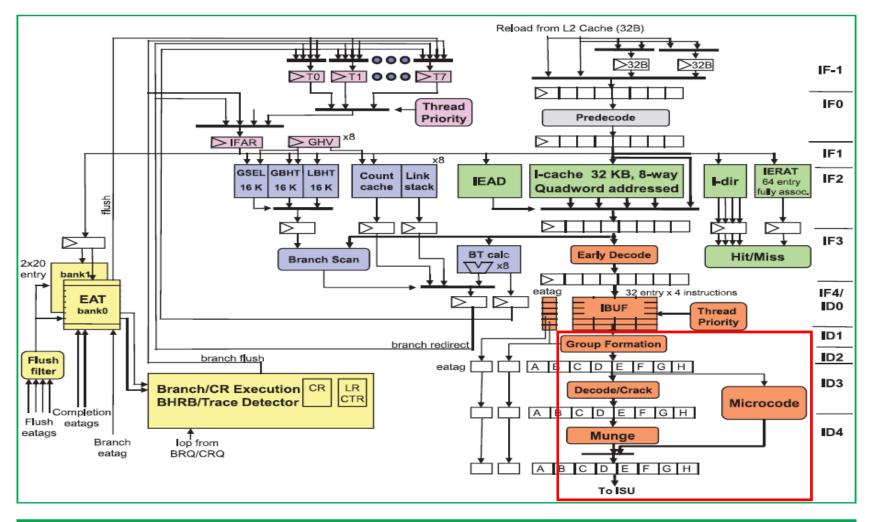

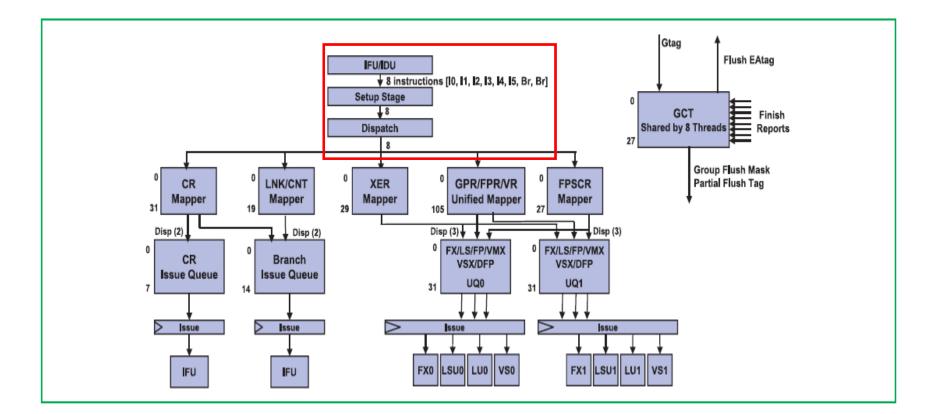

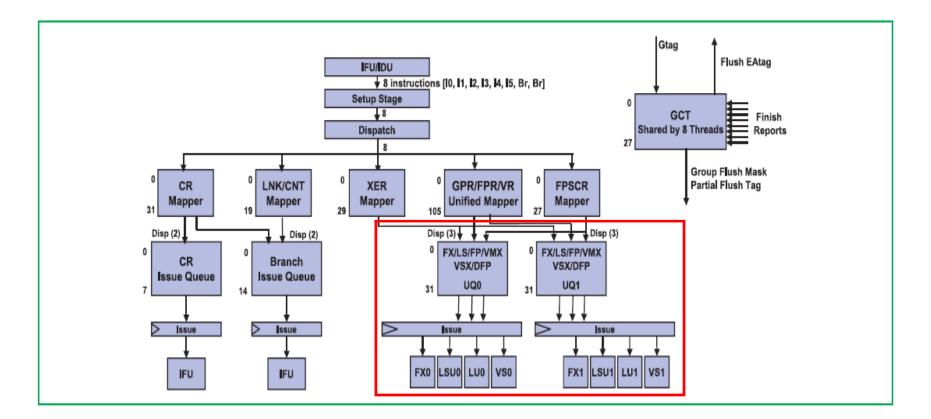

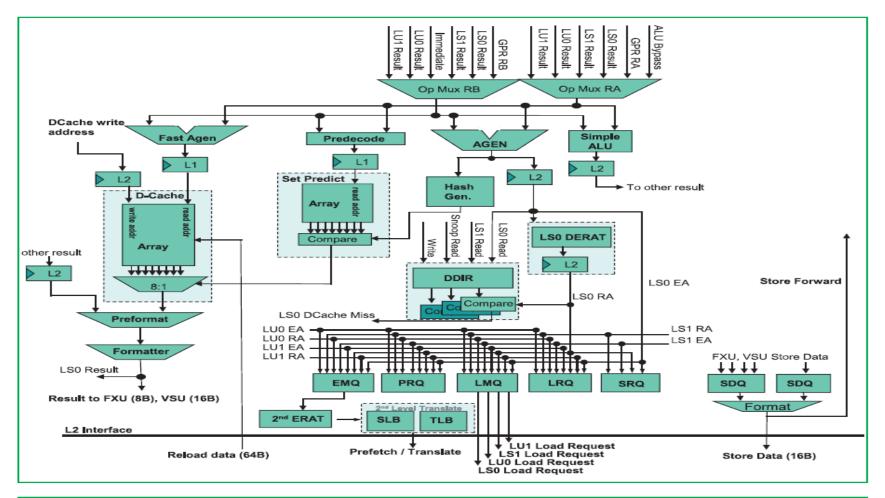

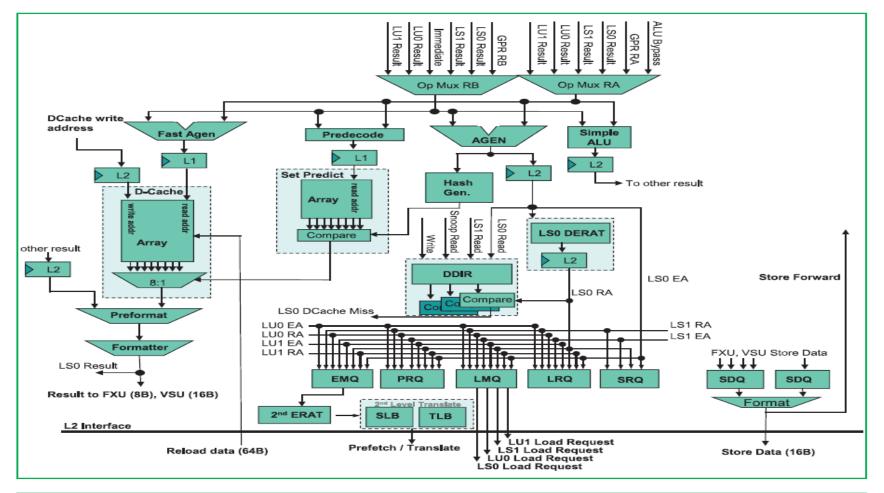

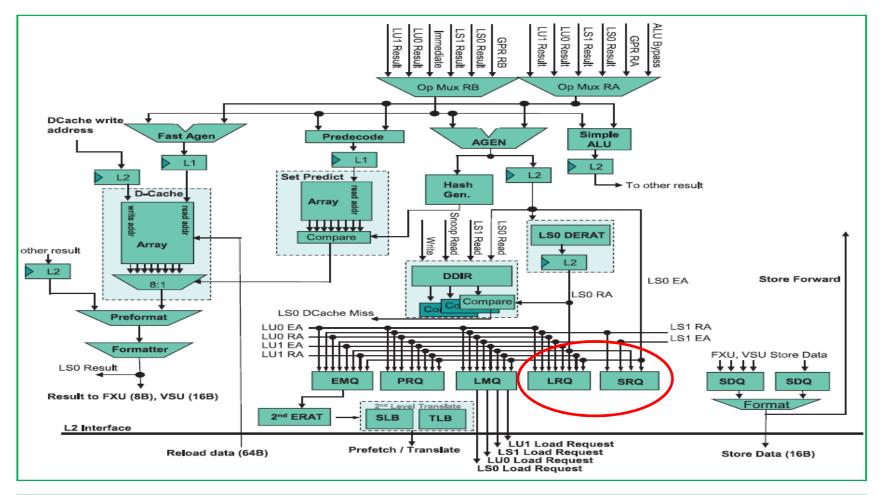

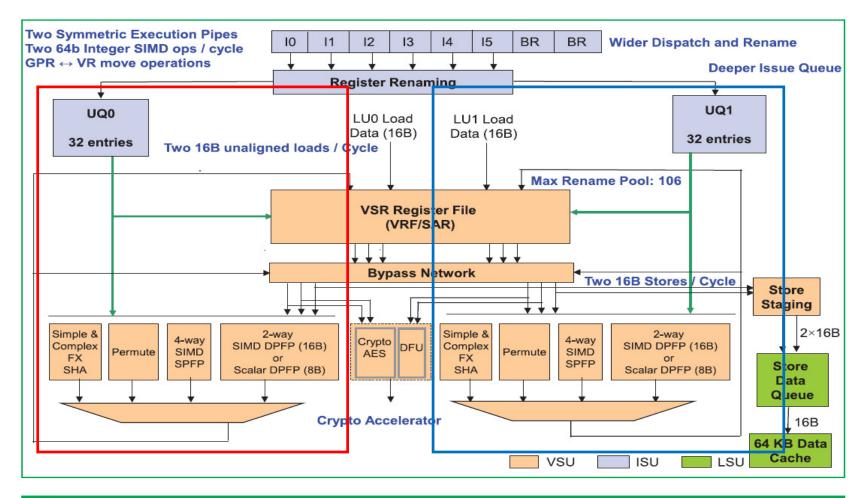

## Figure 2 shows the instruction flow in POWER8 processor core.

#### Figure 2

Instructions flow from the memory hierarchy through various issue queues and then are sent to the functional units for execution.

#### Figure 2

Instructions flow from the memory hierarchy **through various issue queues** and then are sent to the functional units for execution.

#### Figure 2

## Instructions flow from the memory hierarchy through various issue queues and then are sent to the functional units for execution.

#### Figure 2

**Most instructions** (except for branches and condition register logical instructions) **are processed through the Unified Issue Queue (UniQueue),** which consists of two symmetric halves (UQ0 and UQ1).

#### Figure 2

## There are also two copies (not shown) of the general-purpose (GPR0 and GPR1) and vector-scalar (VSR0 and VSR1) physical register files. One copy is

used by instructions processed through UQ0 while the other copy is for instructions processed through UQ1.

#### Figure 2

There are also two copies (not shown) of the general-purpose (GPR0 and GPR1) and vector-scalar (VSR0 and VSR1) physical register files. **One copy is used by instructions processed through UQ0 while the other copy is for instructions processed through UQ1.**

#### Figure 2

The fixed-point, floating-point, vector, load and load-store pipelines are similarly split into **two sets (FX0, FP0, VSX0, VMX0, L0, LS0 in one set**, and **FX1, FP1, VSX1, VMX1, L1, LS1 in the other set)** and each set is associated with one UniQueue half.

#### Figure 2

Which issue queue, physical register file, and functional unit are used by a given instruction **depends on the simultaneous multi-threading mode of the processor core at run time**.

#### Figure 2

In ST mode, the two physical copies of the GPR and VSR have identical contents. Instructions from the thread can be dispatched to either one of the UniQueue halves (UQ0 or UQ1). Load balance across the two UniQueue halves is maintained by dispatching alternate instructions of a given type to alternating UniQueue halves.

#### Figure 2

In the SMT modes (SMT2, SMT4, SMT8), the two copies of the GPR and VSR have different contents. The threads are split into two thread sets and each thread set is restricted to using only one UniQueue half and associated registers and execution pipelines.

#### Figure 2

Fixed-point, floating-point, vector and load/store instructions from even threads (T0, T2, T4, T6) can only be placed in UQ0, can only access GPR0 and VSR0, and can only be issued to FX0, LS0, L0, FP0, VSX0, and VMX0 pipelines.

#### Figure 2

Fixed-point, floating-point, vector and load/store instructions from odd threads (T1, T3, T5, T7) can only be placed in UQ1, can only access GPR1 and VSR1, and can only be issued to FX1, LS1, L1, FP1, VSX1, and VMX1 pipelines.

#### Figure 2

Cryptographic and decimal floating-point instructions from a thread can only be placed in the corresponding UniQueue half, **but since there is only one instance of each of these units, all instructions are issued to the same unit.**

#### Figure 2

Branches and condition register logical instructions have their own dedicated issue queues and execution pipelines, which are shared by all threads.

#### Figure 2

## **Instruction Fetch Unit (IFU)**

Figure 1 shows the POWER8 core floorplan.

The core consists primarily of the following six units: **instruction fetch unit (IFU)**, instruction sequencing unit (ISU), load-store unit (LSU), fixed-point unit (FXU), vector and scalar unit (VSU) and decimal floating point unit (DFU).

The instruction fetch unit contains a 32 KB I-cache (instruction cache) and the load-store unit contains a 64 KB Dcache (data cache), which are both backed up by a tightly integrated 512 KB unified L2 cache.

#### Figure 1

POWER8 processor core floorplan.

## **Instruction Fetch Unit**

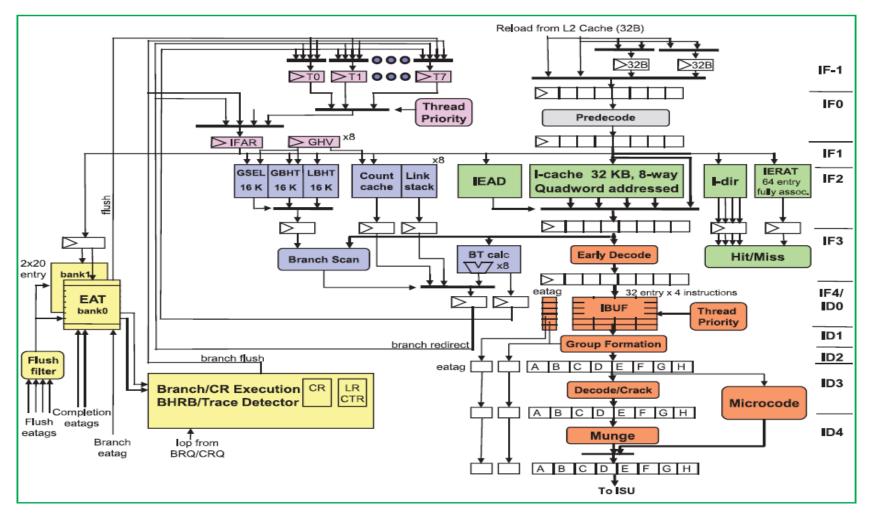

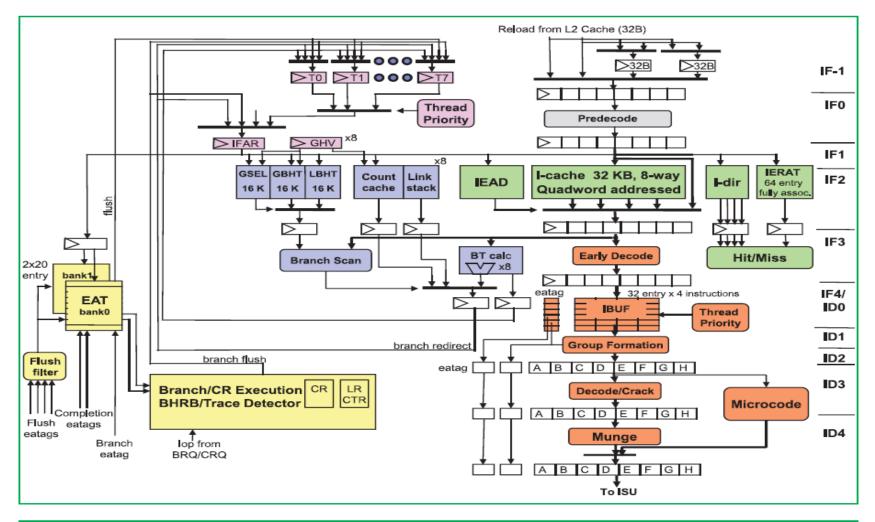

The Instruction Fetch Unit (IFU) in the POWER8 processor (POWER8 IFU) is responsible for feeding the rest of the instruction pipeline with the most likely stream of instructions from each active hardware thread.

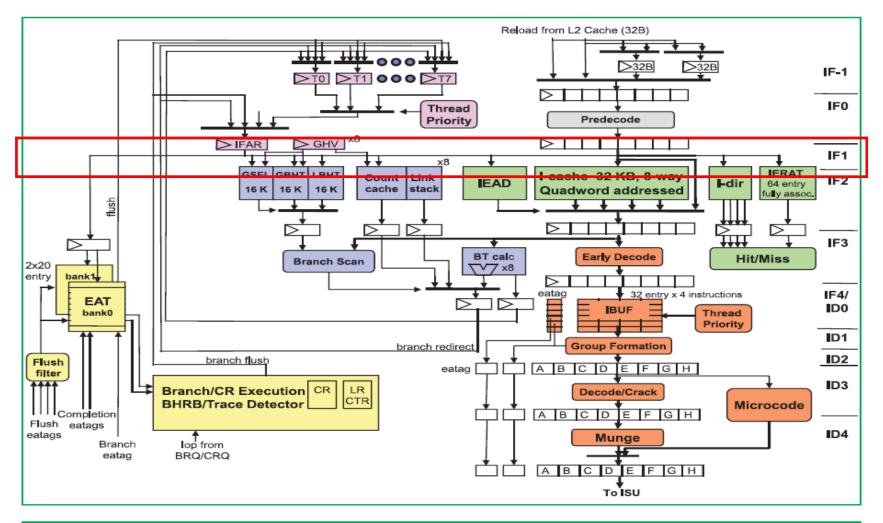

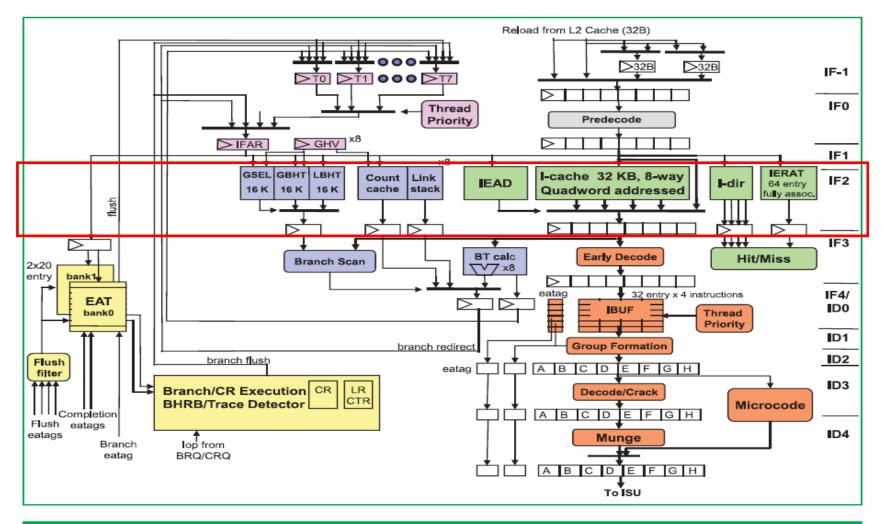

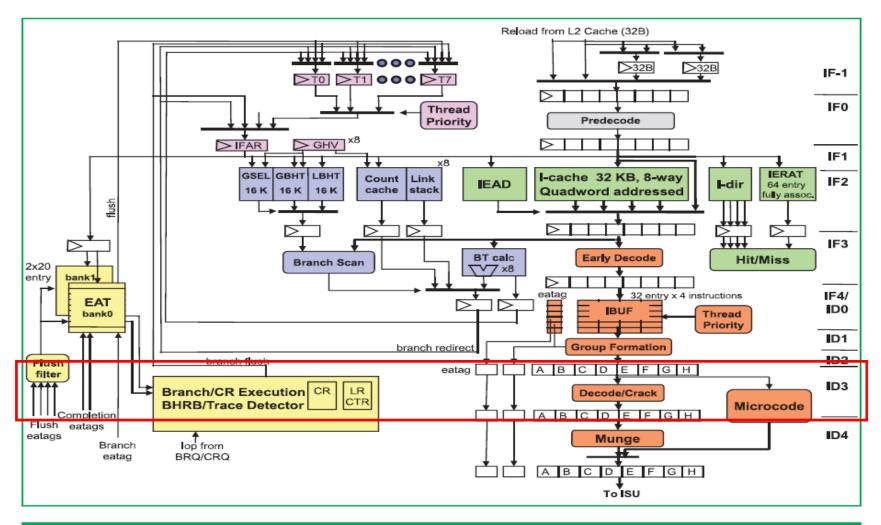

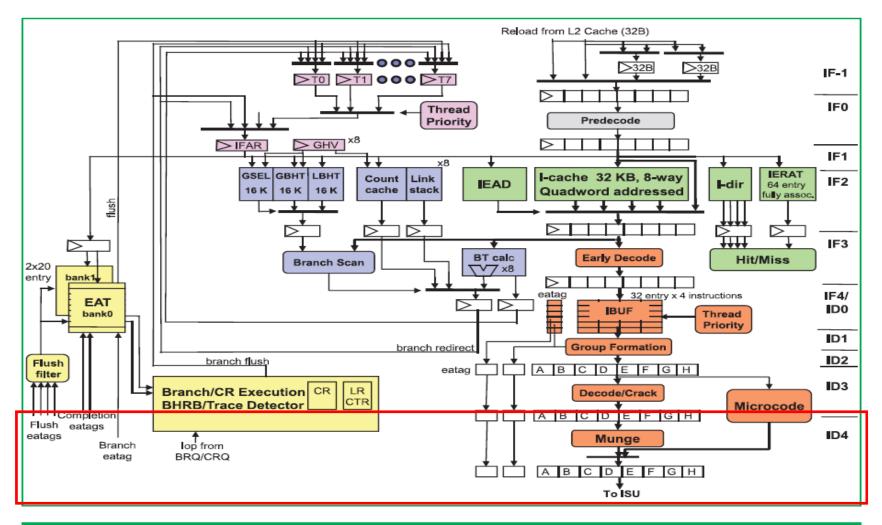

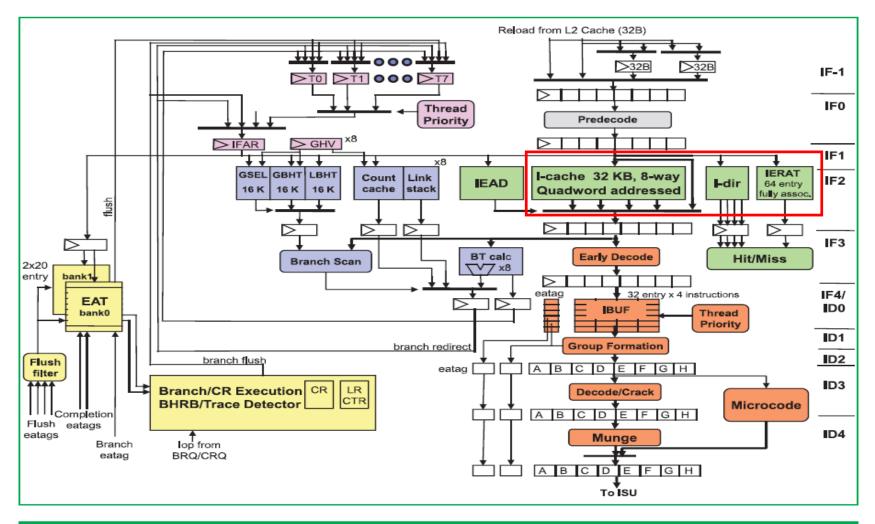

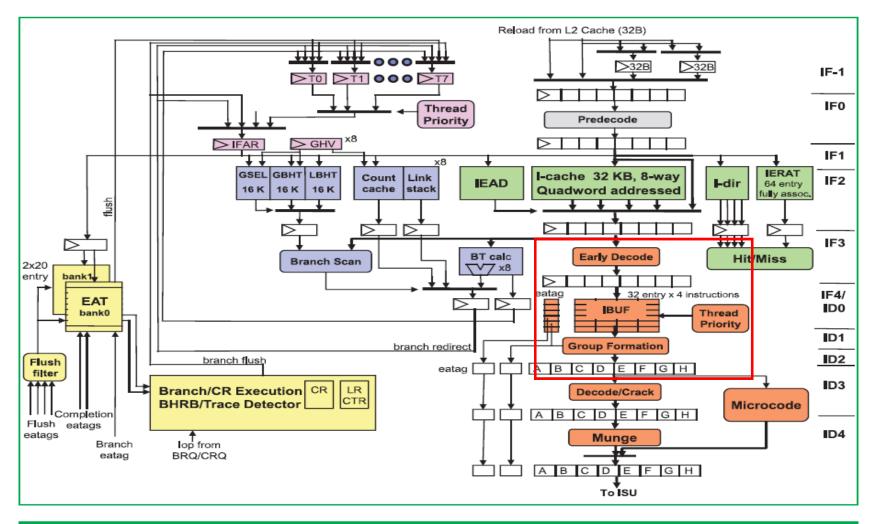

#### Figure 3

POWER8 instruction fetch unit logical flow. The labels on the right of the figure denote the instruction fetch (IF) and instruction decode (ID) stages. (EAT: effective address table, eatag: effective address tag; iop: internal operation.)

It uses branch prediction mechanisms to produce this stream well ahead of the point of execution of the latest committed instruction.

#### Figure 3

POWER8 instruction fetch unit logical flow. The labels on the right of the figure denote the instruction fetch (IF) and instruction decode (ID) stages. (EAT: effective address table, eatag: effective address tag; iop: internal operation.)

The IFU is also responsible for maintaining a balance of instruction execution rates from the active threads using software-specified thread priorities, decoding and forming groups of instructions for the rest of the instruction pipeline, and **executing branch instructions**.

#### Figure 3

### Figure 3

### Figure 3

### Figure 3

### Figure 3

#### Figure 3

### Figure 3

### Figure 3

### Figure 3

### Figure 3

### Figure 3

# **Instruction Fetch Unit (continued)**

The POWER8 IFU has several new features relative to the POWER7 processor IFU. **Support for SMT8 and additional concurrent LPARs** (logical partitions) **required changes in sizes for many resources in the IFU.**

In addition, the following changes were made to improve the overall performance of the POWER8 core:

First, **instruction cache alignment improvements** result in a higher average number of instructions fetched per fetch operation.

Second, **branch prediction mechanism improvements** result in more accurate target and direction predictions.

Third, group formation improvements allow more instructions per dispatch group, on average.

Fourth, instruction address translation hit rates were improved.

Fifth, **instruction fusion is used** to improve performance of certain common instruction sequences.

Finally, **better pipeline hazard avoidance mechanisms** reduce pipeline flushes.

## Instruction fetching and pre-decoding

Fast instruction address translation for instruction fetch is supported by a fully associative 64-entry Instruction Effective to Real Address translation Table (IERAT). The IERAT is shared among all threads.

The IERAT directly supports 4 KB, 64 KB, and 16 MB page sizes. Other page sizes are supported by storing entries with the next smaller supported page size.

The IFU reads instructions into the I-cache from the L2 unified cache. Each read request for instructions from the L2 returns four sectors of 32 bytes each.

These reads are either demand loads that result from I-cache misses or instruction pre-fetches. For each demand load request, the pre-fetch engine initiates additional pre-fetches for sequential cache lines following the demand load.

Demand and pre-fetch requests are made for all instruction threads independently, and instructions may return in any order, including interleaving of sectors for different cache lines.

Up to eight instruction read requests can be outstanding from the core to the L2 cache.

### Figure 3

# Instruction fetching and pre-decoding

Instruction prefetching is supported in ST, SMT2, and SMT4 modes only.

Up to three sequential lines are pre-fetched in ST mode and one sequential line per thread in SMT2 and SMT4 modes.

There is no instruction prefetching in SMT8 mode to save on memory bandwidth.

Pre-fetches are not guaranteed to be fetched and depending on the congestion in the POWER8 processor nest, some pre-fetches may be dropped.

•••

When there are multiple partitions running on the same core (as in the "split core mode" discussed in the Introduction) the fetch cycles are divided equally between the partitions.

If one of the partitions does not have any threads that are ready to fetch, its fetch cycles are relinquished to the next partition that has threads that are ready to fetch.

## **Group formation (of instructions)**

Fetched instructions are processed by the branch scan logic and are also stored in the instruction buffers (IBUF) for group formation.

The IBUF can hold up to 32 entries, each four instructions wide.

Each thread can have four entries in SMT8 mode, eight entries in SMT4 mode and 16 entries in SMT2 and ST modes.

Instructions are retrieved from the IBUF and collected into groups.

Thread priority logic selects one group of up to six non-branch and two branch instructions in ST mode or two groups (from two different threads) of up to three non-branch and one branch instructions in SMT modes per cycle for group formation.

#### Figure 3

## **Instruction decode -- after group formation (of instructions)**

After group formation, the instructions are either decoded or routed to microcode hardware that breaks complex instructions into a series of simple internal operations.

Simple instructions are decoded and sent to dispatch.

Complex instructions that can be handled by two or three simple internal operations are cracked into multiple dispatch slots.

Complex instructions requiring more than three simple internal operations are handled in the microcode engine using a series of simple internal operations.

### Figure 3

# **Instruction Sequencing Unit (ISU)**

Figure 1 shows the POWER8 core floorplan.

The core consists primarily of the following six units: instruction fetch unit (IFU), **instruction sequencing unit (ISU)**, load-store unit (LSU), fixedpoint unit (FXU), vector and scalar unit (VSU) and decimal floating point unit (DFU).

The instruction fetch unit contains a 32 KB I-cache (instruction cache) and the load-store unit contains a 64 KB Dcache (data cache), which are both backed up by a tightly integrated 512 KB unified L2 cache.

### Figure 1

POWER8 processor core floorplan.

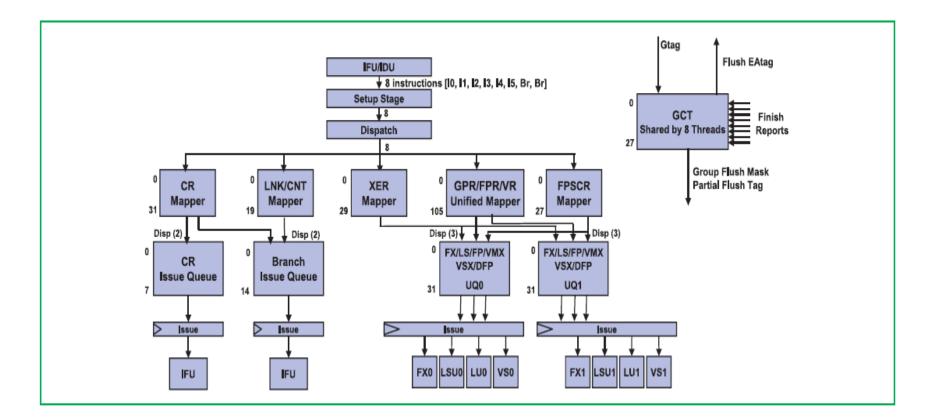

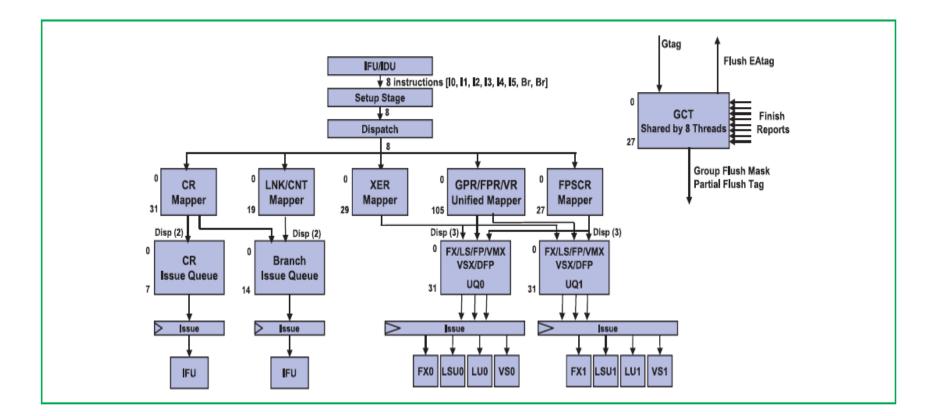

Figure 5 illustrates the logical flow of instructions in the ISU.

### Figure 5

POWER8 instruction sequencing unit (logical flow).

The Instruction Sequencing Unit (ISU) dispatches instructions to the various issue queues, renames registers in support of out-of-order execution, issues instructions from the various issues queues to the execution pipelines, completes executing instructions, and handles exception conditions.

### Figure 5

POWER8 instruction sequencing unit (logical flow).

## Instruction Sequencing Unit (ISU) (continued)

The POWER8 processor dispatches instructions on a group basis.

In ST mode, it can dispatch a group of up to eight instructions per cycle.

In SMT mode, it can dispatch two groups per cycle from two different threads and each group can have up to four instructions.

All resources such as the renaming registers and various queue entries must be available for the instructions in a group before the group can be dispatched.

Otherwise, the group will be held at the dispatch stage.

An instruction group to be dispatched can have at most two branch and six non-branch instructions from the same thread in ST mode. If there is a second branch, it will be the last instruction in the group.

In SMT mode, each dispatch group can have at most one branch and three non-branch instructions.

Figure 5 illustrates the logical flow of instructions in the ISU.

### Figure 5

POWER8 instruction sequencing unit (logical flow).

Figure 5 illustrates the logical flow of instructions in the ISU.

### Figure 5

POWER8 instruction sequencing unit (logical flow).

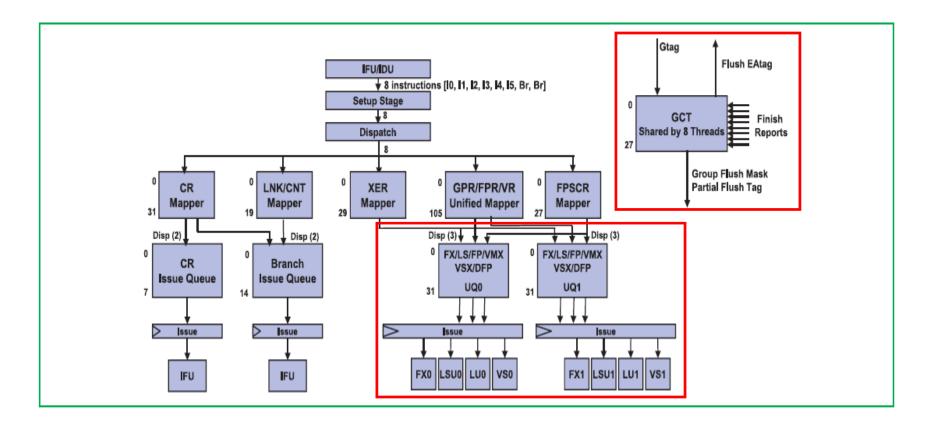

# ISU (and the) Global Completion Table (GCT)

The ISU employs a Global Completion Table (GCT) to track all in-flight instructions after dispatch. The GCT has 28 entries that are dynamically shared by all active threads.

### In ST mode, each GCT entry corresponds to one group of instructions.

In SMT modes, each GCT entry can contain up to two dispatch groups, both from the same thread.

This allows the GCT to track a maximum of 224 in-flight instructions after dispatch.

Figure 5 illustrates the logical flow of instructions in the ISU.

### Figure 5

POWER8 instruction sequencing unit (logical flow).

Instructions flow from the memory hierarchy through various issue queues and then are sent to the functional units for execution.

#### Figure 2

POWER8 processor core pipeline flow. QW-aligned refers to a quadword or 16-byte aligned address.

## ISU (and the) Global Completion Table (GCT) (continued)

Each GCT entry contains finish bits for each instruction in the group. At dispatch, the finish bits are set to reflect the valid instructions.

Instructions are issued out of order and executed speculatively.

When an instruction has executed successfully (without a reject), it is marked as "finished."

When all the instructions in a group are marked "finished," and the group is the oldest for a given thread, the group can "complete."

When a group completes, the results of all its instructions are made architecturally visible and the resources held by its instructions are released.

# ISU (and the) Global Completion Table (GCT) (continued)

In ST mode, only one group, consisting of up to eight instructions, can complete per cycle.

In SMT modes, the POWER8 core can complete one group per thread set per cycle, for a maximum total of two group completions per cycle.

When a group is completed, a completion group tag (GTAG) is broadcast so that resources associated with the completing group can be released and reused by new instructions.

# The missing tuning factor: ST/SMT-2/-4/-8 threading mode

### • We've been watching the **AIX:vmstat** -**IWw 1:cpu:pc**|:ec values

System configuration: lcpu=24 mem=98304MB ent=3.50

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                      | kthr                                                                                                                                                                                                                                                                                                                 | memory                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                        | page                                                  | faults                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | сри                                                  | time                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                      | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                 | 10603753   13740     10620193   7681     10615392   7983     10614238   7600     10615800   11800     10619720   10024     10619541   11802     10625852   8871     10625852   8871     10625865   8225     1062666   7520     10627603   7530     10650842   8024     1065552   9025     10651811   10365     10658461   7441     10663679   11152 | 208898   190     229049   66     208767   200     170112   79     283700   39     176554   211     260671   175     218591   73     204261   203     196040   129     170450   269     280327   65     278207   17     235577   67     240955   157     269364   146     274516   100     251368   169 | $\begin{array}{cccccccccccccccccccccccccccccccccccc$  | 322458 21610 34255 421693   424420 23268 35204 47365 4   577709 27767 40485 68236 3   381740 16645 23758 27180 3   508624 18288 56699 50940 5   416103 18099 27871 32296 3   438619 21385 35251 41714 3   438075 24327 34351 52368 3   439267 24022 41875 51451 3   511750 16995 26588 27617 2   516765 16093 35379 26578 2   522790 20146 45574 42703 3   545004 20127 39842 37642 3   525465 17350 59493 27922 3   526103 16200 74331 26622 2   582747 20175 67976 40111 3   462540 16155 84832 25935 2                                                          | $\begin{array}{cccccccccccccccccccccccccccccccccccc$ | 5.96 170.3 07:45:50<br>5.96 170.3 07:45:51<br>5.96 170.4 07:45:52<br>5.94 169.6 07:45:53<br>5.95 170.0 07:45:54<br>5.95 170.0 07:45:55<br>5.97 170.6 07:45:56<br>5.98 170.7 07:45:57<br>5.96 170.4 07:45:57<br>5.96 170.4 07:45:58<br>5.93 169.3 07:45:59<br>5.94 169.7 07:46:02<br>5.99 171.1 07:46:03<br>5.94 169.8 07:46:04<br>5.94 169.8 07:46:05<br>5.94 169.9 07:46:07<br>5.95 169.9 07:46:08<br>5.91 168.9 07:46:10         |

| 87 130 0 484 10662862 7645 243972 167 0 0 241235 442606 19228 29701 36625 34 66 0 0 5.96 170.2 07:46:13   73 214 0 270 10669973 7617 208389 134 0 0 218368 451905 20355 37358 43749 43 57 0 0 5.96 170.2 07:46:14   64 169 0 350 10669921 7555 225201 117 0 0 226223 354926 21032 41807 41315 37 63 0 0 5.95 170.0 07:46:16   78 170 0 276 10689099 7661 226187 145 0 0 237468 415431 19934 32417 42240 41 59 0 6.04 172.5 07:46:18   139 144 0 536 10690574 8024 185162 226 0 183546 607865 | kthr                                                                                                                                                                                                                                                                                                                 | memory                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                        | page                                                  | faults                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | сри                                                  | time                                                                                                                                                                                                                                                                                                                                                                                                                               |

| ער איז איז ארא איז ארא איז ארא איז איז איז איז איז איז איז איז איז אי                                                                                                                                                                                                                                                                                                                                                                                                                        | 61 176 0 306<br>87 130 0 484<br>73 214 0 270<br>64 169 0 350<br>24 218 0 391<br>78 170 0 276<br>139 144 0 536<br>101 161 0 403<br>95 238 0 402<br>86 179 0 370<br>107 173 0 324<br>50 216 0 714<br>93 220 0 418<br>37 217 0 598<br>70 205 0 546<br>60 217 0 428<br>27 242 0 390<br>0 0 0 432<br>69 212 0 527<br>kthr | 10662515 10066   10660046 10750   10662862 7645   10669973 7617   10669921 7555   10676954 9836   10690574 8024   1069958 7616   10700104 10392   10698534 9452   10698380 7610   10698534 9452   10698380 7610   10691688 7525   10698380 7740   10703911 8824   10705976 7520   1070620 7558   10707620 7558   10709781 7992   memory memory      | 283292   179     220960   208     243972   167     208389   134     225201   117     209241   51     226187   145     185162   226     264120   22     198493   214     251838   47     199484   225     189307   255     213037   101     198431   44     215674   99                                 | $ \begin{array}{cccccccccccccccccccccccccccccccccccc$ | 442606 19228 29701 36625 3<br>451905 20355 37358 43749 4<br>354926 21032 41807 41315 3<br>475267 21227 51247 44534 3<br>415431 19934 32417 42240 4<br>607865 25510 35254 68076 3<br>314681 18946 28118 34260 3<br>559791 23737 31972 71900 3<br>248156 19971 28538 38416 3<br>437450 24024 36601 61687 3<br>526700 23571 38127 55190 4<br>379842 23297 32474 50401 3<br>422083 23904 41602 55736 3<br>337136 24801 36854 55341 2<br>473692 25275 34238 63691 3<br>420118 22340 45530 43630 4<br>387871 23063 38031 49638 3<br>445210 23583 44806 52071 4<br>faults | $\begin{array}{cccccccccccccccccccccccccccccccccccc$ | 5.96 170.2 07:46:13<br>5.96 170.2 07:46:14<br>5.97 170.6 07:46:15<br>5.95 170.0 07:46:16<br>5.99 168.1 07:46:17<br>6.04 172.5 07:46:18<br>5.93 169.5 07:46:19<br>5.95 169.9 07:46:20<br>6.00 171.6 07:46:21<br>5.95 170.0 07:46:22<br>5.98 170.8 07:46:23<br>5.97 170.5 07:46:24<br>5.97 170.5 07:46:25<br>5.97 170.5 07:46:25<br>5.97 170.5 07:46:27<br>5.97 170.5 07:46:28<br>5.97 170.5 07:46:28<br>5.96 170.4 07:46:30<br>time |

# The missing tuning factor: ST/SMT-2/-4/-8 threading mode

- The :pc | :ec values tell us how much CPU is used and the ec%, or CPUbusy%

- Next, it is clear the POWER8 core has markedly improved threading capability

- Perhaps now we should begin working with the missing tuning factor too, and not just use the :pc | :ec values to monitor CPU utilization

| page |     | faults |                |       |       |       |      |      | c  | pu | time |       |          |

|------|-----|--------|----------------|-------|-------|-------|------|------|----|----|------|-------|----------|

| pi   | ро  | fr     | sr             | in    | sy    | cs us | s sy | / id | wa |    | рс   | ec h  | r mi se  |

| . 0  | . 0 | 209880 | 474371         | 23305 | 32689 | 49347 |      |      | 0  | 0  | 5.97 | 170.6 | 07:45:49 |

| 0    | 0   | 235597 | 324458         | 21610 | 34255 | 42169 | 39   | 61   | 0  | 0  | 5.96 | 170.3 | 07:45:50 |

| 0    | 0   | 217973 | 424420         | 23268 | 35204 | 47365 | 41   | 59   | 0  | 0  | 5.96 | 170.3 | 07:45:51 |

| 0    | 0   | 165232 | 5777 <b>09</b> | 27767 | 40485 | 68236 | 36   | 62   | 0  | 2  | 5.96 | 170.4 | 07:45:52 |

| 0    | 0   | 280305 | 381740         | 16645 | 23758 | 27180 | 30   | 70   | 0  | 0  | 5.94 | 169.6 | 07:45:53 |

| 0    | 0   | 202322 | 508624         | 18288 | 56699 | 50940 | 50   | 49   | 0  | 2  | 5.95 | 170.0 | 07:45:54 |

| 0    | 0   | 247113 | 416103         | 18099 | 27871 | 32296 | 34   | 66   | 0  | 1  | 5.95 | 170.0 | 07:45:55 |

| 0    | 0   | 220304 | 436819         | 21385 | 35251 | 41714 | 36   | 64   | 0  | 0  | 5.97 | 170.6 | 07:45:56 |

| 0    | 0   | 200149 | 438075         | 24327 | 34351 | 52368 | 37   | 63   | 0  | 0  | 5.98 | 170.7 | 07:45:57 |

| 0    | 0   | 200242 | 439267         | 24022 | 41875 | 51451 | 38   | 62   | 0  | 0  | 5.96 | 170.4 | 07:45:58 |

| 0    | 0   | 183842 | 352926         | 14443 | 65697 | 37923 | 51   | 45   | 0  | 4  | 5.93 | 169.3 | 07:45:59 |

| 0    | 0   | 271484 | 511750         | 16995 | 26588 | 27617 | 27   | 73   | 0  | 0  | 5.94 | 169.7 | 07:46:00 |

| 0    | 0   | 276192 | 516765         | 16093 | 35379 | 26578 | 29   | 71   | 0  | 0  | 5.92 | 169.2 | 07:46:02 |

| 0    | 0   | 235086 | 5227 <b>90</b> | 20146 | 45574 | 42703 | 32   | 68   | 0  | 0  | 5.99 | 171.1 | 07:46:03 |

| 0    | 0   | 256486 | 545004         | 20127 | 39842 | 37642 | 30   | 70   | 0  | 0  | 5.94 | 169.6 | 07:46:04 |

| 0    | 0   | 275012 | 525465         | 17350 | 59493 | 27922 | 30   | 70   | 0  | 0  | 5.94 | 169.8 | 07:46:05 |

| 0    | 0   | 281271 | 526103         | 16200 | 74331 | 26622 | 28   | 72   | 0  | 0  | 5.94 | 169.8 | 07:46:07 |

| 0    | 0   | 245856 | 582747         | 20175 | 67976 | 40111 | 32   | 68   | 0  | 0  | 5.95 | 169.9 | 07:46:08 |

| 0    | 0   | 291276 | 462540         | 16155 | 84832 | 25935 | 29   | 71   | 0  | 0  | 5.91 | 168.9 |          |

| 0    | 0   | 228257 | 625080         | 21903 | 86171 | 45734 | 35   | 65   | 0  | 0  | 5.98 | 170.9 | 07:46:10 |

| page |     |        |                | fa    | ults  |       |      |      | C  | pu |      |       | time     |

| pi   | ро  | fr     | sr             | in    | sy    | cs us | s sy | / id | wa |    | рс   | ec h  | rmise    |

# The missing tuning factor: ST/SMT-2/-4/-8 threading mode

- We should begin tuning POWER8 with more attention to its innate capability

- Tuning POWER8 by :pc and :ec% values alone is missing a deeper dimension

- We should begin controlling an ignored factor; I will call it "SMT threadedness"

- Too often I find workloads barely able to a keep a thread active on a core

- A POWER core can show great productivity -- but only if we push it harder

- Do we agree that compelling more work from our investment is a good thing?

- Do you want to see what I mean? Sure, no problem.

- What can you distinguish between the top and bottom on the next slide?

# **AIX: vmstat** –**IWw** 1: Which is more CPUcore efficient?

| Sys                                                                                                              | tem c                                                                                                | onfi                                                          | igura                                                                                                                                   | tion: lcpu=24                                                                                                                                                                                                                                                 | mem=9830                                                                                                                                                   | )4MB ent                                                                                                                                                                                                             | =3.50                                                                                                                                   |                                                                                                   |                                                                |                                                                                                                                                                        |                                                                                                                                                                                                            |                                                                                                                                                                         |                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                |                                                                                              |                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                             |

|------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|----------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                  | kthr memory                                                                                          |                                                               |                                                                                                                                         | page                                                                                                                                                                                                                                                          |                                                                                                                                                            |                                                                                                                                                                                                                      | faults                                                                                                                                  |                                                                                                   |                                                                |                                                                                                                                                                        | ct                                                                                                                                                                                                         | ou                                                                                                                                                                      | time                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                |                                                                                              |                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                             |

| 135<br>88<br>74<br>1111<br>75<br>80<br>79<br>107<br>70<br>18<br>138<br>113<br>99<br>109<br>103<br>84<br>4<br>102 | 212<br>179<br>195<br>308<br>171<br>139<br>140<br>123<br>134<br>222<br>237<br>251<br>68<br>218<br>187 | 000000000000000000000000000000000000000                       | w<br>376<br>408<br>508<br>623<br>616<br>494<br>661<br>494<br>661<br>492<br>652<br>472<br>3334<br>494<br>248<br>250<br>334<br>279<br>338 | avm<br>10599516<br>10603753<br>10620193<br>10615392<br>10614238<br>10615800<br>10619720<br>10619720<br>10619741<br>10622884<br>10625852<br>10625100<br>10629865<br>10627603<br>10645179<br>10650842<br>10655552<br>10651811<br>10658461<br>10663679<br>memory | 13740<br>7681<br>7983<br>7600<br>11800<br>10024<br>11802<br>7771<br>8871<br>11543<br>8225<br>7520<br>7530<br>7530<br>7596<br>8024<br>9025<br>10365<br>7441 | fi<br>208898<br>229049<br>208767<br>170112<br>283700<br>176554<br>260671<br>218591<br>204261<br>196040<br>170450<br>280327<br>278207<br>278207<br>278207<br>240955<br>269364<br>274516<br>251368<br>285750<br>220862 | fo<br>190<br>66<br>200<br>79<br>39<br>211<br>175<br>73<br>203<br>129<br>269<br>65<br>17<br>67<br>157<br>146<br>100<br>169<br>164<br>322 | pi<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0 |                                                                | 235597<br>217973<br>165232<br>280305<br>202322<br>247113<br>220304<br>200149<br>200242<br>183842<br>276192<br>235086<br>256486<br>275012<br>281271<br>245856<br>291276 | sr<br>474371<br>324458<br>424420<br>577709<br>381740<br>508624<br>416103<br>436819<br>438075<br>439267<br>352926<br>511750<br>516765<br>522790<br>545004<br>522465<br>526103<br>582747<br>462540<br>625080 | 21610<br>23268<br>27767<br>16645<br>18288<br>18099<br>21385<br>24327<br>24022<br>14443<br>16995<br>16093<br>20146<br>20127<br>17350<br>16200<br>20175<br>16155<br>21903 | 34255<br>35204<br>40485<br>23758<br>56699<br>27871<br>35251<br>34351<br>41875<br>65697<br>26588<br>35379<br>45574<br>39493<br>74331<br>67976<br>84832 | cs us sy<br>49347 40 6<br>42169 39 6<br>47365 41 5<br>68236 36 6<br>27180 30 7<br>50940 50 4<br>32296 34 6<br>41714 36 6<br>52368 37 6<br>51451 38 6<br>51451 38 6<br>37923 51 4<br>27617 27 7<br>26578 29 7<br>42703 32 6<br>37642 30 7<br>27922 30 7<br>26622 28 7<br>40111 32 6<br>25935 29 7<br>45734 35 6 | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                         | $\begin{array}{ccccccc} 0 & 5.96 \\ 0 & 5.96 \\ 2 & 5.96 \\ 0 & 5.94 \\ 2 & 5.95 \\ 1 & 5.95 \\ 0 & 5.97 \\ 0 & 5.98 \\ 0 & 5.98 \\ 0 & 5.94 \\ 0 & 5.94 \\ 0 & 5.94 \\ 0 & 5.94 \\ 0 & 5.94 \\ 0 & 5.95 \\ 0 & 5.91 \\ 0 & 5.98 \end{array}$ | ec hr mi se<br>170.6 07:45:49<br>170.3 07:45:50<br>170.3 07:45:51<br>170.4 07:45:52<br>169.6 07:45:53<br>170.0 07:45:55<br>170.6 07:45:55<br>170.6 07:45:55<br>170.6 07:45:55<br>170.7 07:45:55<br>169.3 07:45:59<br>169.7 07:46:00<br>169.2 07:46:03<br>169.6 07:46:04<br>169.8 07:46:04<br>169.8 07:46:05<br>169.8 07:46:07<br>169.9 07:46:08<br>168.9 07:46:09<br>170.9 07:46:10<br>time |

| r                                                                                                                | b                                                                                                    | р                                                             | w                                                                                                                                       | avm                                                                                                                                                                                                                                                           | fre                                                                                                                                                        | fi                                                                                                                                                                                                                   | fo                                                                                                                                      | рі                                                                                                | ро                                                             | fr                                                                                                                                                                     | sr                                                                                                                                                                                                         | in                                                                                                                                                                      | sy                                                                                                                                                    | cs us sy                                                                                                                                                                                                                                                                                                       | id wa                                                                                        | рс                                                                                                                                                                                                                                            | ec hr mi se                                                                                                                                                                                                                                                                                                                                                                                 |

| Syst                                                                                                             |                                                                                                      |                                                               | gurat                                                                                                                                   | ion: lcpu=64                                                                                                                                                                                                                                                  | mem=983(                                                                                                                                                   | 04MB ent                                                                                                                                                                                                             | =2.00                                                                                                                                   |                                                                                                   |                                                                |                                                                                                                                                                        |                                                                                                                                                                                                            |                                                                                                                                                                         |                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                |                                                                                              |                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                                                  | kthr                                                                                                 |                                                               |                                                                                                                                         | memory                                                                                                                                                                                                                                                        |                                                                                                                                                            |                                                                                                                                                                                                                      | page                                                                                                                                    |                                                                                                   |                                                                |                                                                                                                                                                        | faults                                                                                                                                                                                                     |                                                                                                                                                                         |                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                |                                                                                              | сри                                                                                                                                                                                                                                           | time                                                                                                                                                                                                                                                                                                                                                                                        |

| r<br>0<br>16<br>12<br>12<br>12<br>12<br>10<br>11<br>8                                                            | b<br>0<br>1<br>2<br>1<br>2<br>2<br>2<br>2<br>2                                                       | P<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0 | <b>w</b><br>0<br>4<br>4<br>4<br>2<br>4<br>2<br>4<br>2<br>4                                                                              | avm<br>13157874<br>13159509<br>13157043<br>13160790<br>13156803<br>13156883<br>13156834<br>13156834<br>13156834                                                                                                                                               | fre<br>104956<br>101976<br>102588<br>97452<br>99825<br>97990<br>95549<br>93249<br>89791                                                                    | fi<br>938<br>1308<br>1857<br>1384<br>1613<br>1756<br>2501<br>2287<br>3447                                                                                                                                            | fo<br>51<br>36<br>60<br>8<br>14<br>7<br>46<br>50<br>65                                                                                  | рі<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0                                                   | ро<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0 | fr<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0                                                                                                         | 5r<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0                                                                                                                                                  | in<br>1151<br>1099<br>1041<br>450<br>486<br>658<br>825<br>794<br>1414<br>568                                                                                            | sy<br>31013<br>19090<br>13968<br>79248<br>13369<br>80019<br>6014<br>14215<br>7407<br>5845                                                             | 4398 61<br>3397 61<br>3638 61<br>4007 61<br>4327 62<br>4372 61<br>5589 61                                                                                                                                                                                                                                      | 5 24<br>3 32<br>3 36<br>2 37<br>2 37<br>2 37<br>2 36<br>2 37<br>2 36<br>2 37<br>2 36         | 0 10.89<br>0 10.96<br>0 11.62<br>0 11.65<br>0 10.84<br>0 10.27<br>0 10.50<br>0 10.07<br>0 10.91                                                                                                                                               | 548.0 22:30:05<br>581.2 22:30:06<br>582.7 22:30:07<br>541.9 22:30:08<br>513.3 22:30:09<br>525.0 22:30:10                                                                                                                                                                                                                                                                                    |